**iSBC 544**

**INTELLIGENT COMMUNICATIONS**

**CONTROLLER BOARD**

**HARDWARE REFERENCE MANUAL**

Manual Order Number: 9800616B

Revision B incorporates the logic necessary

to use Intel 2732 PROMs. The authority for the

change is ECO No. 2-2945.

The information in this document is subject to change without notice.

Intel Corporation makes no warranty of any kind with regard to this material, including, but not limited to, the implied warranties of merchantability and fitness for a particular purpose. Intel Corporation assumes no responsibility for any errors that may appear in this document. Intel Corporation makes no commitment to update nor to keep current the information contained in this document.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Intel Corporation.

The following are trademarks of Intel Corporation and may be used only to describe Intel products:

ICE

INSITE

INTEL

INTELLEC

iSBC

LIBRARY MANAGER

MCS

MEGACHASSIS

MICROMAP

MULTIBUS

PROMPT

RMX

UPI

μSCOPE

## PREFACE

This manual provides general information, preparation for use, programming information, principles of operation, and service information for the iSBC 544 Intelligent Communications Controller Board. Supplementary information is provided in the following documents:

- Intel MULTIBUS Interfacing, Application Note AP-28.

- Intel MCS-85 User's Manual, Order No. 9800366.

- Intel 8080 Microcomputer Peripherals User's Manual, Order No. 98-364.

- Intel 8080/8085 Assembly Language Programming Manual, Order 98-301.

# CONTENTS

|                                               | PAGE |                                                           | PAGE |  |

|-----------------------------------------------|------|-----------------------------------------------------------|------|--|

| <b>CHAPTER 1</b>                              |      |                                                           |      |  |

| <b>GENERAL INFORMATION</b>                    |      |                                                           |      |  |

| Introduction .....                            | 1-1  | Memory Addressing .....                                   | 3-5  |  |

| Description .....                             | 1-1  | I/O Addressing .....                                      | 3-5  |  |

| Serial I/O Ports .....                        | 1-1  | 8253 PIT Programming .....                                | 3-7  |  |

| Parallel I/O Port .....                       | 1-2  | Mode Control Word Count .....                             | 3-7  |  |

| Programmable Timers .....                     | 1-2  | Addressing .....                                          | 3-8  |  |

| Interrupt Functions .....                     | 1-2  | Initialization .....                                      | 3-9  |  |

| 8085A CPU .....                               | 1-2  | Operation .....                                           | 3-9  |  |

| PROM Configuration .....                      | 1-3  | Clock Frequency/Divide Ratio Selection .....              | 3-10 |  |

| RAM Configuration .....                       | 1-3  | Synchronous Mode .....                                    | 3-10 |  |

| Equipment Supplied .....                      | 1-3  | Rate Generator/Interval Timer .....                       | 3-11 |  |

| Specifications .....                          | 1-3  | Interrupt Timer .....                                     | 3-11 |  |

| <b>CHAPTER 2</b>                              |      |                                                           |      |  |

| <b>PREPARATION FOR USE</b>                    |      |                                                           |      |  |

| Introduction .....                            | 2-1  | 8259 PIC Programming .....                                | 3-12 |  |

| Unpacking and Inspection .....                | 2-1  | Interrupt Priority Modes .....                            | 3-12 |  |

| Installation Considerations .....             | 2-1  | Interrupt Mask .....                                      | 3-12 |  |

| User Furnished Components .....               | 2-1  | Status Read .....                                         | 3-12 |  |

| Power Requirements .....                      | 2-1  | Initialization Command Words .....                        | 3-13 |  |

| Cooling Requirements .....                    | 2-3  | Operation Command Words .....                             | 3-13 |  |

| Physical Dimensions .....                     | 2-3  | Addressing .....                                          | 3-13 |  |

| Component Installation .....                  | 2-3  | Initialization .....                                      | 3-13 |  |

| EPROM Chips .....                             | 2-3  | Operation .....                                           | 3-16 |  |

| Rise Time/Noise Capacitors .....              | 2-3  | 8155 Programmable Peripheral Interface and Timer .....    | 3-19 |  |

| Jumper Configurations .....                   | 2-4  | 8155 I/O Port Programming .....                           | 3-19 |  |

| PROM Configuration .....                      | 2-4  | Port A Programming .....                                  | 3-21 |  |

| On-Board RAM .....                            | 2-4  | Port B and C Programming .....                            | 3-21 |  |

| Priority Interrupts .....                     | 2-8  | 8155 Timer Programming .....                              | 3-21 |  |

| Counter Clock Frequency .....                 | 2-8  | 8251A USART Programming .....                             | 3-24 |  |

| Serial I/O Clocks .....                       | 2-8  | Mode Instruction Format .....                             | 3-24 |  |

| Serial I/O Port Interface .....               | 2-9  | Sync Characters .....                                     | 3-26 |  |

| Parallel I/O Port .....                       | 2-9  | Command Instruction Format .....                          | 3-26 |  |

| Input Options .....                           | 2-9  | Reset .....                                               | 3-26 |  |

| Output Options .....                          | 2-9  | Addressing .....                                          | 3-26 |  |

| Data Set Conversion .....                     | 2-9  | Initialization .....                                      | 3-26 |  |

| Multibus Configuration .....                  | 2-9  | Operation .....                                           | 3-28 |  |

| Signal Characteristics .....                  | 2-10 | 8085A Interrupt Handling .....                            | 3-30 |  |

| Power Fail/Memory Protect Configuration ..... | 2-16 | TRAP Interrupt .....                                      | 3-30 |  |

| Serial I/O Cabling .....                      | 2-16 | RST 7.5, 6.5, and 5.5 Inputs .....                        | 3-30 |  |

| Parallel I/O Cabling .....                    | 2-19 | Interrupts Handled by RST 7.5, RST 6.5, and RST 5.5 ..... | 3-31 |  |

| Board Installation .....                      | 2-19 | Master Mode .....                                         | 3-32 |  |

| <b>CHAPTER 3</b>                              |      |                                                           |      |  |

| <b>PROGRAMMING INFORMATION</b>                |      |                                                           |      |  |

| Introduction .....                            | 3-1  | INTR Interrupt .....                                      | 3-32 |  |

| Intelligent Slave Concept .....               | 3-1  | 8085A Interrupt Generation .....                          | 3-32 |  |

| Intelligent Slave Programming .....           | 3-1  | <b>CHAPTER 4</b>                                          |      |  |

| System Programming .....                      | 3-1  | <b>PRINCIPLES OF OPERATION</b>                            |      |  |

| On-Board Programming .....                    | 3-4  | Introduction .....                                        | 4-1  |  |

| System Initialization .....                   | 3-4  | Functional Description .....                              | 4-1  |  |

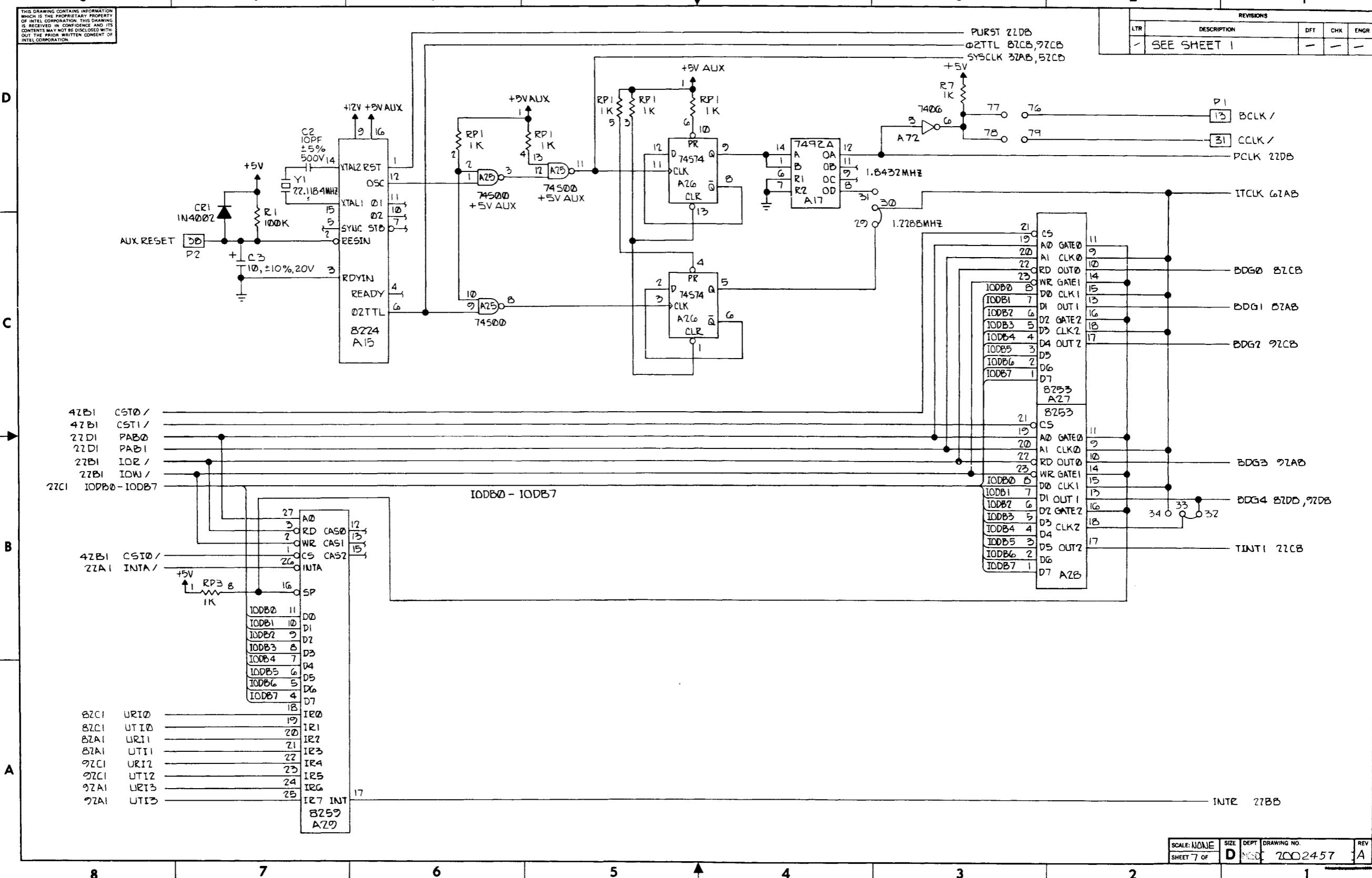

|                                               |      | Clock Circuits .....                                      | 4-1  |  |

|                                               |      | 8085A Central Processor Unit .....                        | 4-1  |  |

|                                               |      | Interval Timer and Baud Rate Generators .....             | 4-1  |  |

|                                               |      | Serial I/O Ports .....                                    | 4-1  |  |

|                                               |      | Parallel I/O Ports .....                                  | 4-1  |  |

|                                               |      | Interrupt Control .....                                   | 4-2  |  |

|                                    | PAGE |                                | PAGE |

|------------------------------------|------|--------------------------------|------|

| PROM Configuration.....            | 4-2  | APPENDIX A                     |      |

| RAM Configuration.....             | 4-2  | 8085A INSTRUCTION SET          |      |

| Bus Interface .....                | 4-2  |                                |      |

| Dual Port Control.....             | 4-2  |                                |      |

| Master Mode .....                  | 4-2  |                                |      |

| Circuit Analysis.....              | 4-2  |                                |      |

| Initialization .....               | 4-3  | APPENDIX B                     |      |

| Clock Circuits .....               | 4-3  | TELETYPE WRITER MODIFICATIONS  |      |

| 8085A CPU Timing.....              | 4-3  |                                |      |

| Address Bus .....                  | 4-9  |                                |      |

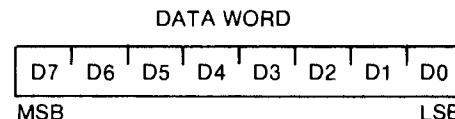

| Data Bus.....                      | 4-9  |                                |      |

| Read/Write Command Generation..... | 4-9  |                                |      |

| Dual Port Control Logic .....      | 4-11 | APPENDIX C                     |      |

| Off Board Memory Request.....      | 4-12 | CUSTOM PROGRAMMED PROMS        |      |

| I/O Operation .....                | 4-12 |                                |      |

| ROM/PROM Operation .....           | 4-12 | Introduction .....             | C-1  |

| RAM Operation .....                | 4-13 | Chip Select PROM.....          | C-1  |

| Interrupt Operation .....          | 4-14 | Chip Select PROM Outputs ..... | C-2  |

## CHAPTER 5 SERVICE INFORMATION

|                                     |     |

|-------------------------------------|-----|

| Introduction.....                   | 5-1 |

| Replaceable Parts .....             | 5-1 |

| Service Diagrams.....               | 5-1 |

| Service and Repair Assistance ..... | 5-1 |

## TABLES

| TABLE | TITLE                                      | PAGE | TABLE | TITLE                                       | PAGE |

|-------|--------------------------------------------|------|-------|---------------------------------------------|------|

| 1-1   | Specifications.....                        | 1-3  | 3-6   | Typical PIT Counter Read Subroutine.....    | 3-10 |

| 2-1   | User Furnished and Installed Components .. | 2-1  | 3-7   | PIT Count Value Vs Rate Multiplier for Each |      |

| 2-2   | User Furnished Connector Details .....     | 2-2  |       | Baud Rate.....                              | 3-11 |

| 2-3   | Jumper Selectable Options.....             | 2-4  | 3-8   | PIT Rate Generator Frequencies and Timer    |      |

| 2-4   | Multibus Connector P1 Pin Assignments...   | 2-10 |       | Intervals .....                             | 3-11 |

| 2-5   | Multibus Signal Functions .....            | 2-11 | 3-9   | PIT Time Intervals Vs Time Counts .....     | 3-15 |

| 2-6   | iSBC 544 DC Characteristics - Slave Mode . | 2-12 | 3-10  | PIC Device Address Insertion .....          | 3-13 |

| 2-7   | iSBC 544 DC Characteristics - Master Mode  | 2-13 | 3-11  | Typical PIC Initialization Subroutine.....  | 3-16 |

| 2-8   | iSBC 544 AC Characteristics - Slave Mode . | 2-14 | 3-12  | PIC Operation Procedures.....               | 3-16 |

| 2-9   | iSBC 544 AC Characteristics - Master Mode  | 2-15 | 3-13  | Typical PIC Interrupt Request Register Read |      |

| 2-10  | Auxiliary Connector P2 Pin Assignments ..  | 2-16 |       | Subroutine .....                            | 3-18 |

| 2-11  | Connector J1-J4 RS232C Signal Interface .. | 2-17 | 3-14  | Typical PIC In-Service Register Read        |      |

| 2-12  | Connector J5 Parallel Output Signal        |      |       | Subroutine .....                            | 3-18 |

|       | Interface.....                             | 2-18 | 3-15  | Typical PIC Set Mask Register Subroutine .  | 3-18 |

| 3-1   | iSBC 544 On-Board Memory Address .....     | 3-5  | 3-16  | Typical PIC Mask Register Read Subroutine   | 3-18 |

| 3-2   | I/O Address Assignments .....              | 3-6  | 3-17  | Typical PIC End-of-Interrupt Command        |      |

| 3-3   | 8253 PIT Counter Outputs.....              | 3-7  |       | Subroutine .....                            | 3-19 |

| 3-4   | Typical PIT Control Word Subroutine.....   | 3-9  | 3-18  | Typical 8155 Initialize Routine .....       | 3-20 |

| 3-5   | Typical PIT Count Value Load Subroutine .. | 3-9  | 3-19  | Typical Command Register Load Routine ..    | 3-21 |

| TABLE | TITLE                                                          | PAGE | TABLE | TITLE                                                  | PAGE |

|-------|----------------------------------------------------------------|------|-------|--------------------------------------------------------|------|

| 3-20  | Typical I/O Port Programming Routines . . . . .                | 3-22 | C-2   | Chip Select Addressing . . . . .                       | C-1  |

| 3-21  | Baud Rates Vs Count Lengths . . . . .                          | 3-23 | C-3   | PROM Page Partitioning . . . . .                       | C-2  |

| 3-22  | Typical 8155 Timer Routine. . . . .                            | 3-24 | C-4   | Chip Select Decode PROM Outputs (2K of ROM). . . . .   | C-2  |

| 3-23  | Typical USART Mode or Command Instruction Subroutine . . . . . | 3-27 | C-5   | Chip Select Decode PROM Outputs (4K of ROM). . . . .   | C-3  |

| 3-24  | Typical USART Data Character Read Subroutine . . . . .         | 3-28 | C-6   | Chip Select Decode PROM Outputs (I/O Chips) . . . . .  | C-3  |

| 3-25  | Typical USART Data Character Write Subroutine . . . . .        | 3-28 | C-7   | RAM Base Address . . . . .                             | C-4  |

| 3-26  | Typical USART Status Read Subroutine . . . . .                 | 3-29 | C-8   | RAM Size . . . . .                                     | C-4  |

| 3-27  | Interrupt Vector Memory Locations. . . . .                     | 3-30 | C-9   | RAM Size-PROM Page . . . . .                           | C-4  |

| 3-28  | Typical RST 7.5 Interrupt Routine . . . . .                    | 3-31 | C-10  | Address Transformation PROM Output (4K RAM) . . . . .  | C-5  |

| 3-29  | PINT and RINT Flop Reset Routine . . . . .                     | 3-31 | C-11  | Address Transformation PROM Output (8K RAM) . . . . .  | C-5  |

| 4-1   | CPU Status and Control Lines . . . . .                         | 4-4  | C-12  | Address Transformation PROM Output (16K RAM) . . . . . | C-6  |

| 5-1   | Replaceable Parts . . . . .                                    | 5-1  |       |                                                        |      |

| 5-2   | List of Manufacturers' Codes . . . . .                         | 5-3  |       |                                                        |      |

| C-1   | Chip Select Coding. . . . .                                    | C-1  |       |                                                        |      |

## ILLUSTRATIONS

| FIGURE | TITLE                                                                    | PAGE | FIGURE | TITLE                                                        | PAGE |

|--------|--------------------------------------------------------------------------|------|--------|--------------------------------------------------------------|------|

| 1-1    | iSBC 544 Intelligent Communications Controller Board . . . . .           | 1-1  | 3-16   | Synchronous Mode Transmission Format . . . . .               | 3-25 |

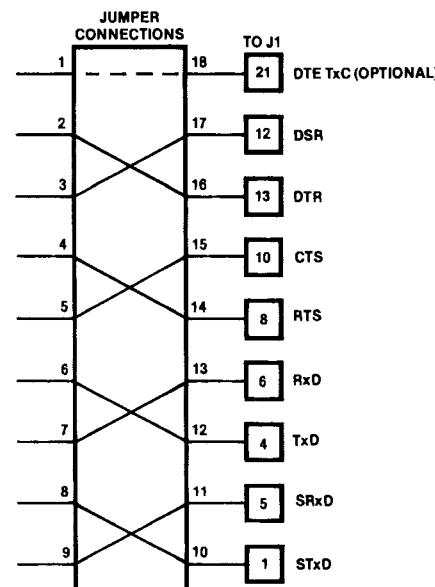

| 2-1    | Reconfigured DIP Header Jumper Assembly for Data Set Operation . . . . . | 2-9  | 3-17   | Asynchronous Mode Instruction Word Format . . . . .          | 3-25 |

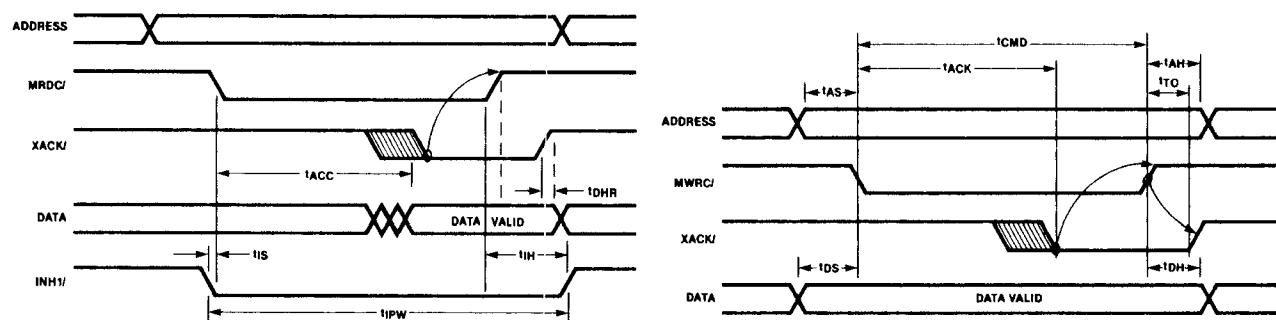

| 2-2    | Bus Exchange Timing . . . . .                                            | 2-14 | 3-18   | Asynchronous Mode Transmission Format . . . . .              | 3-25 |

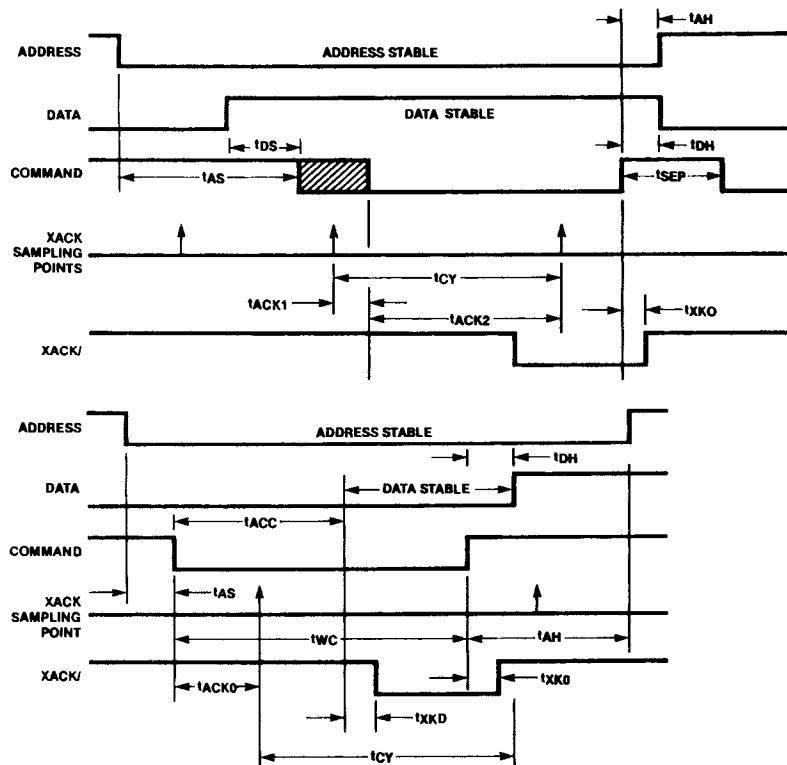

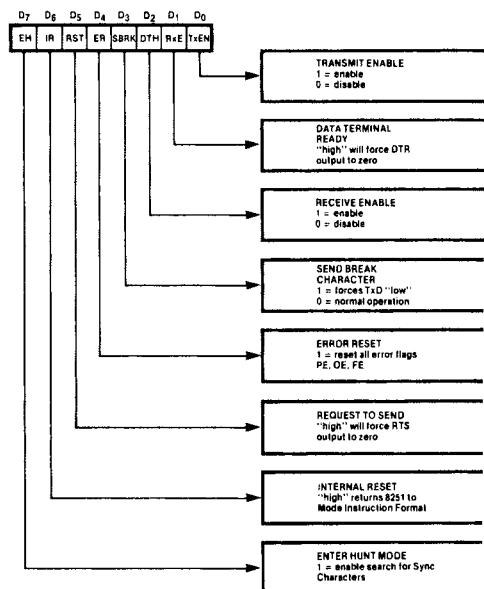

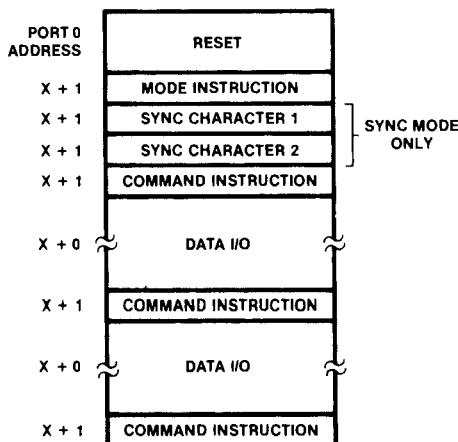

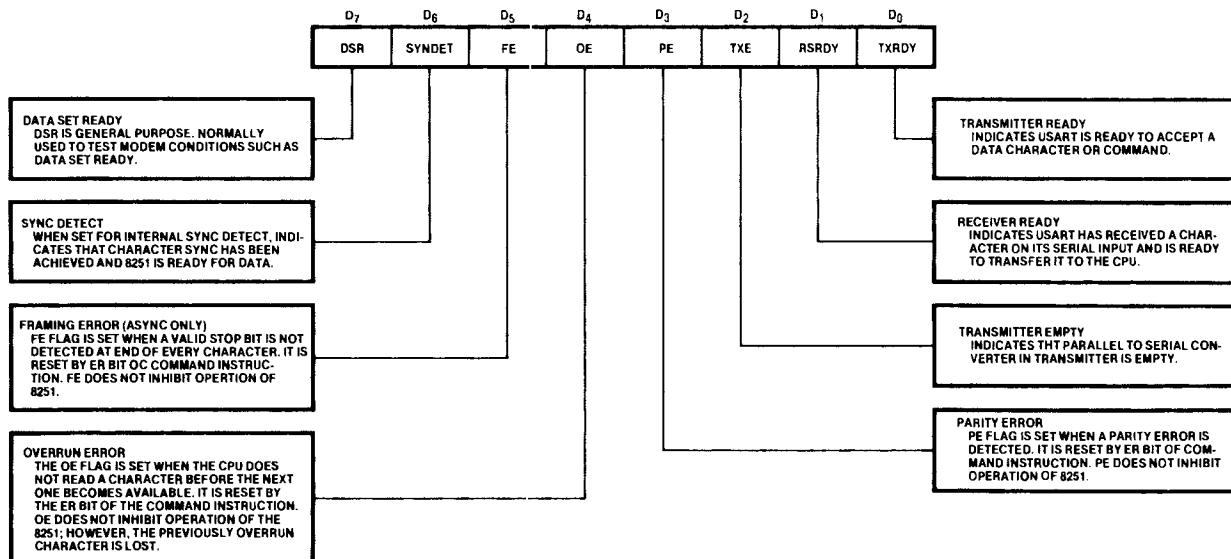

| 2-3    | Bus Control Timing . . . . .                                             | 2-15 | 3-19   | USART Command Instruction Word Format . . . . .              | 3-26 |

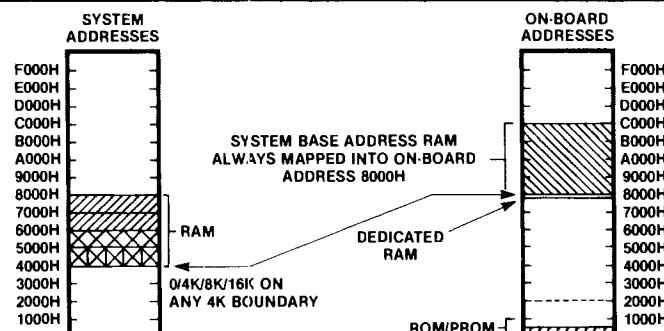

| 3-1    | iSBC 544 Memory Addressing . . . . .                                     | 3-2  | 3-20   | Typical USART Initialization and Data I/O Sequence . . . . . | 3-27 |

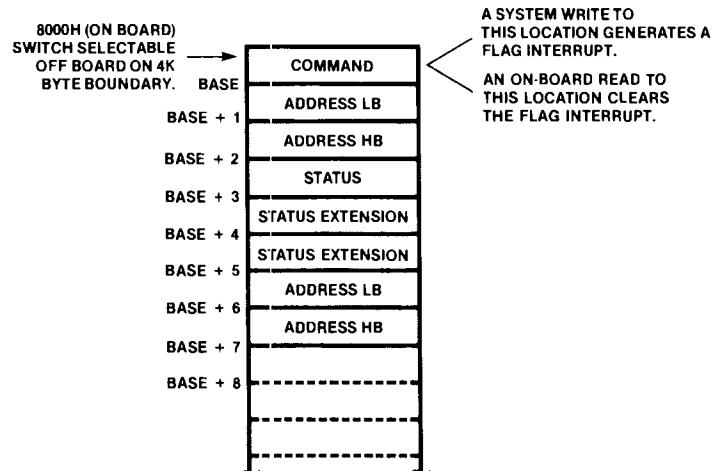

| 3-2    | Communications Area . . . . .                                            | 3-2  | 3-21   | USART Status Read Format . . . . .                           | 3-29 |

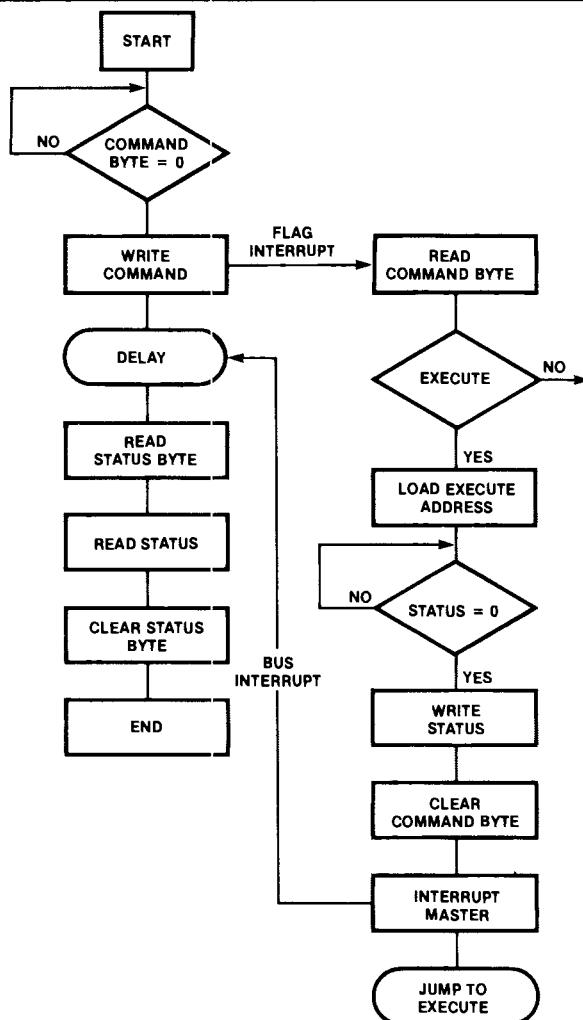

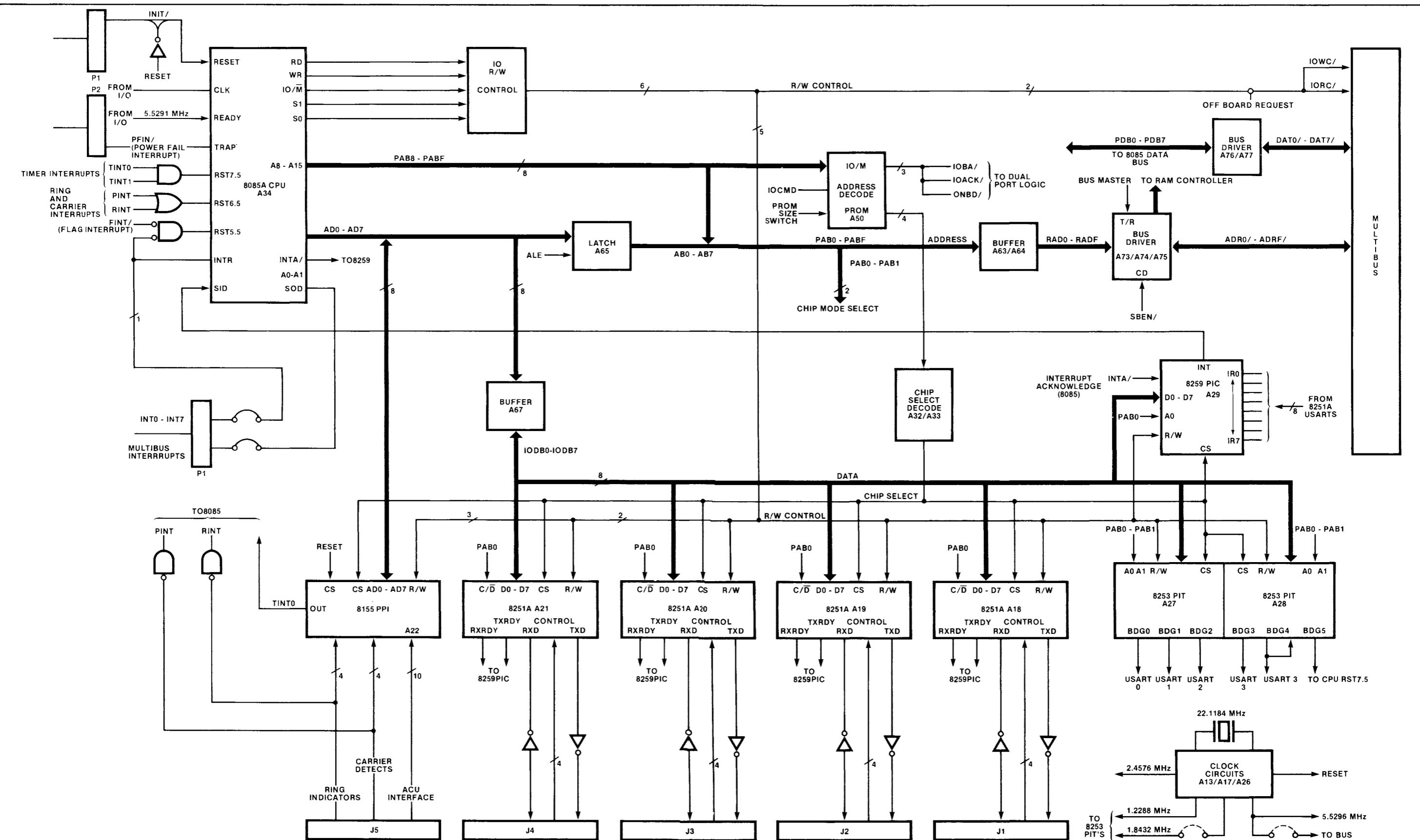

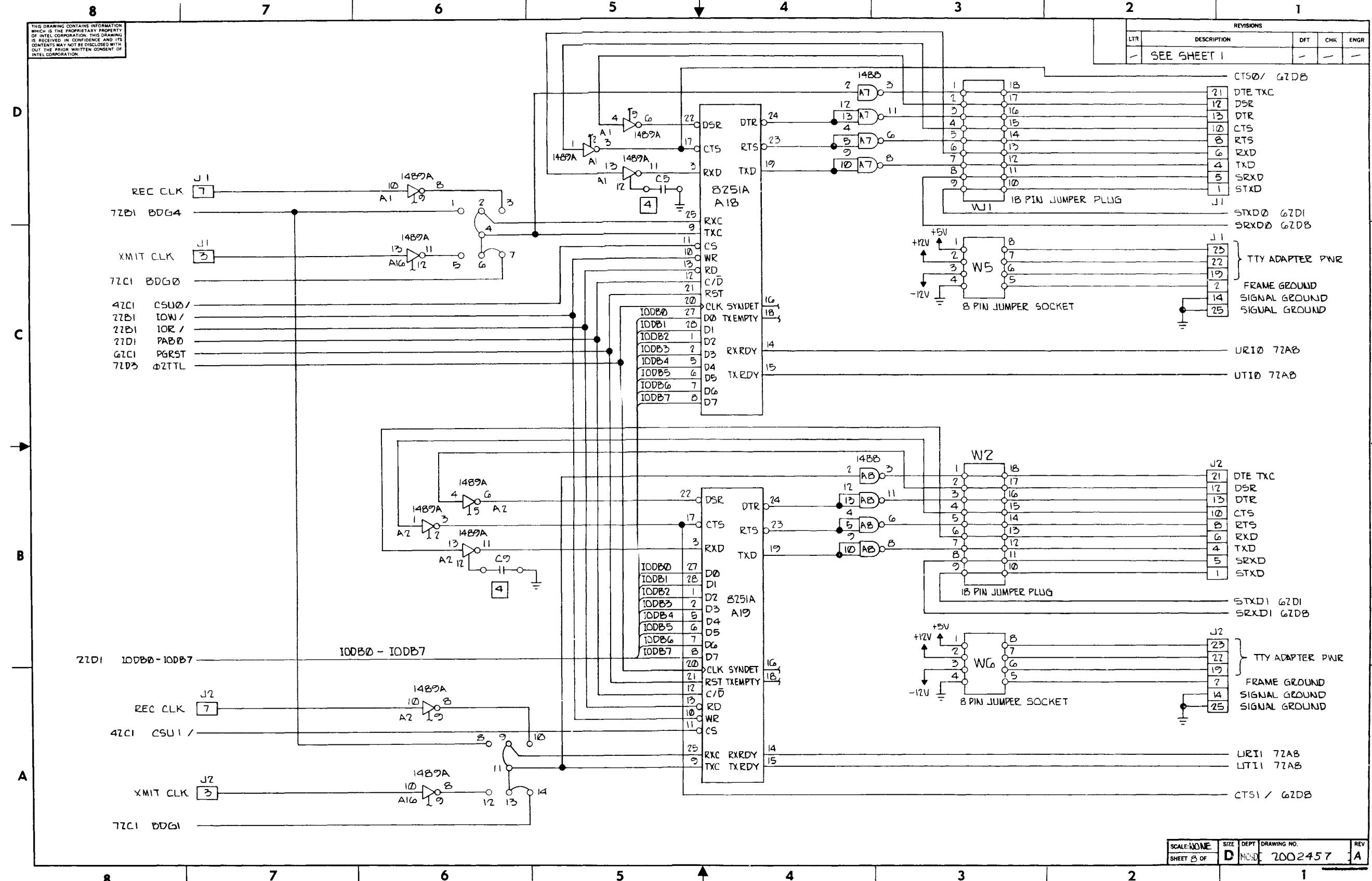

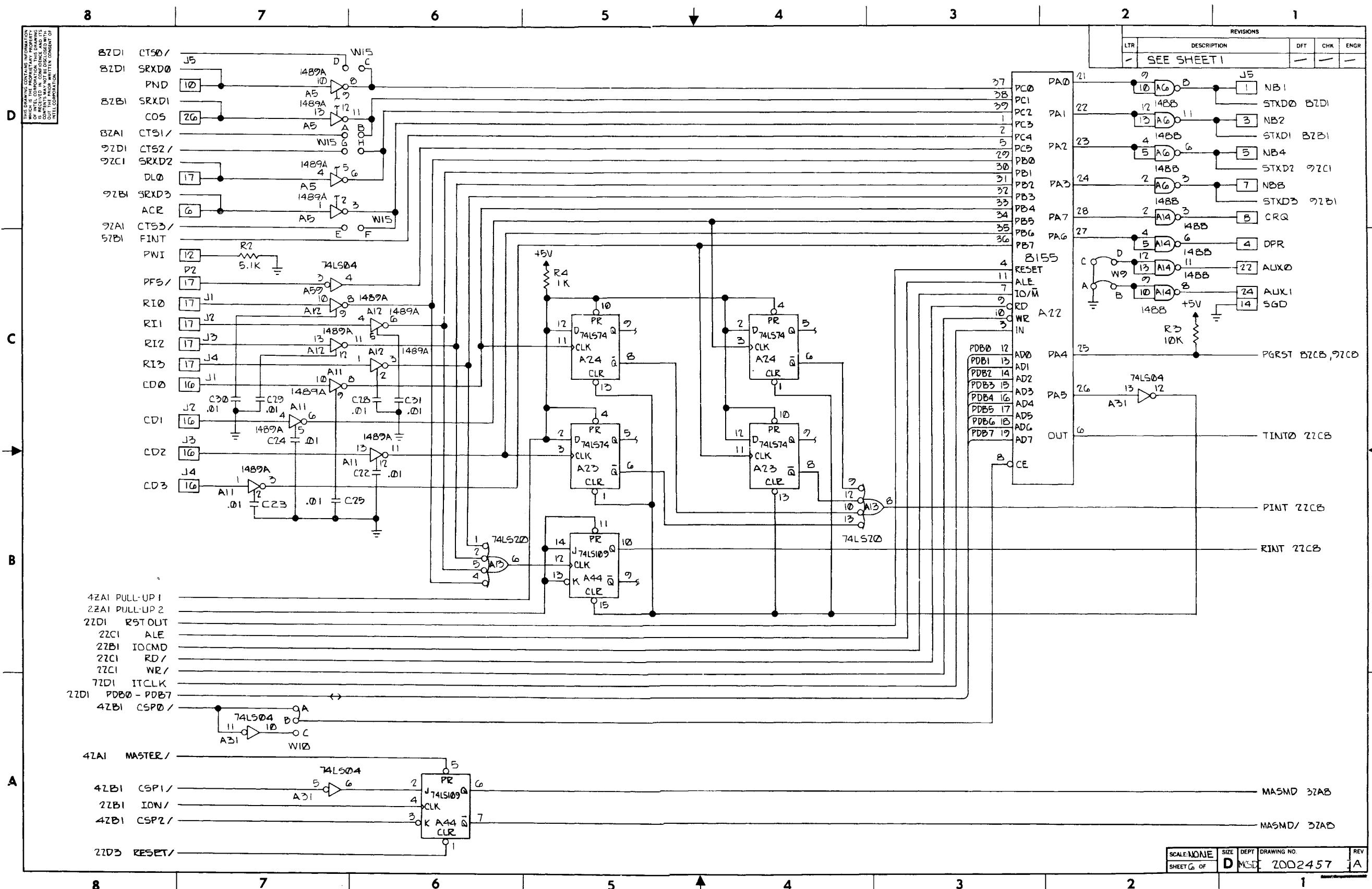

| 3-3    | Communications Program Flow Chart . . . . .                              | 3-4  | 4-1    | iSBC 544 Input/Output and Interrupt Block Diagram . . . . .  | 4-15 |

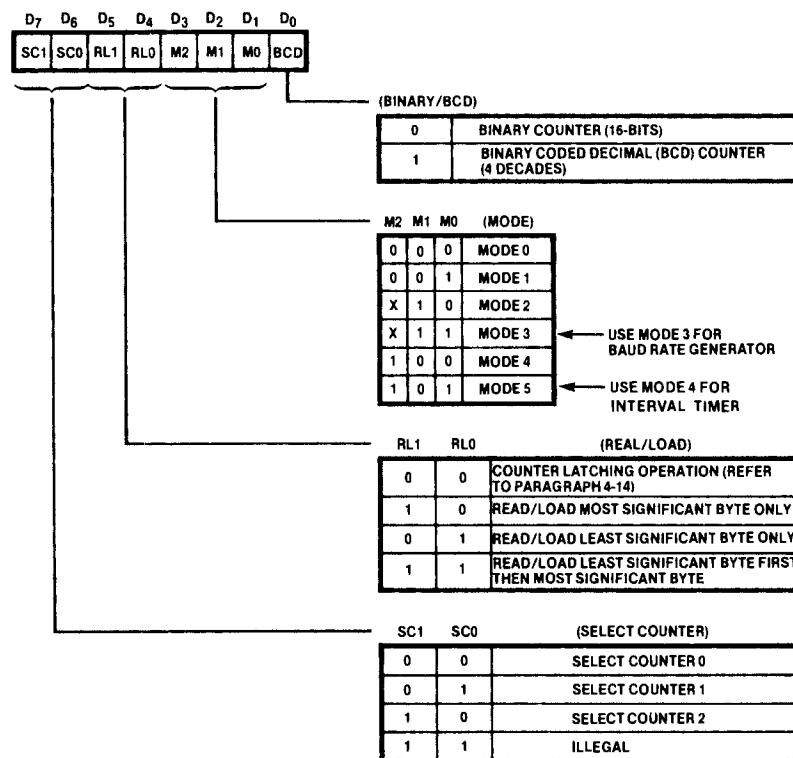

| 3-4    | PIT Mode Control Word Format . . . . .                                   | 3-7  | 4-2    | iSBC 544 Memory Block Diagram . . . . .                      | 4-17 |

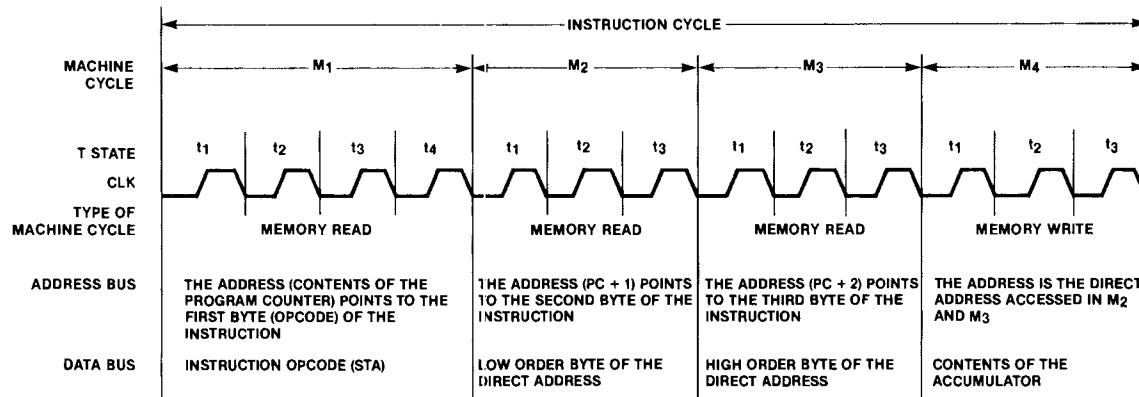

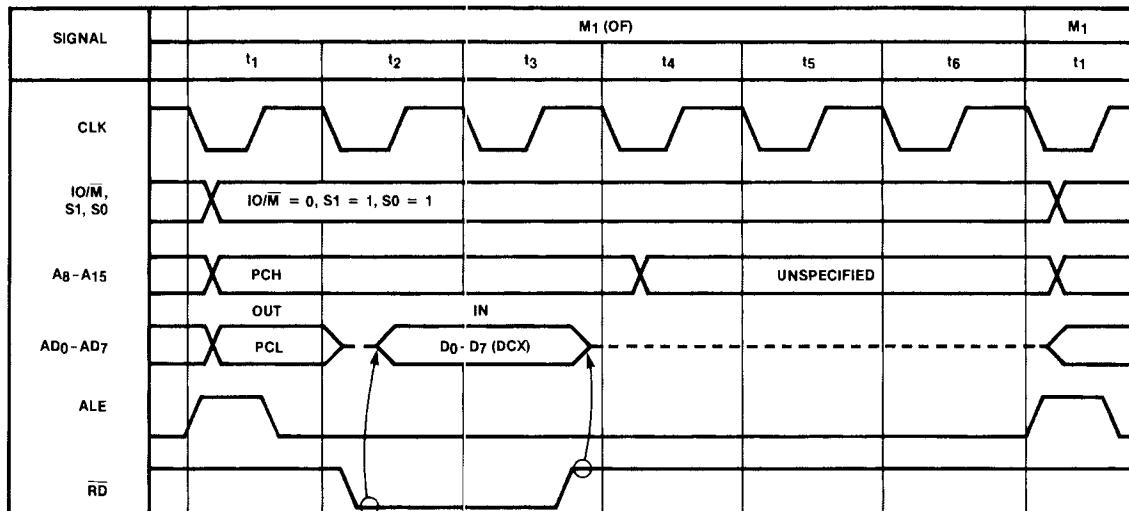

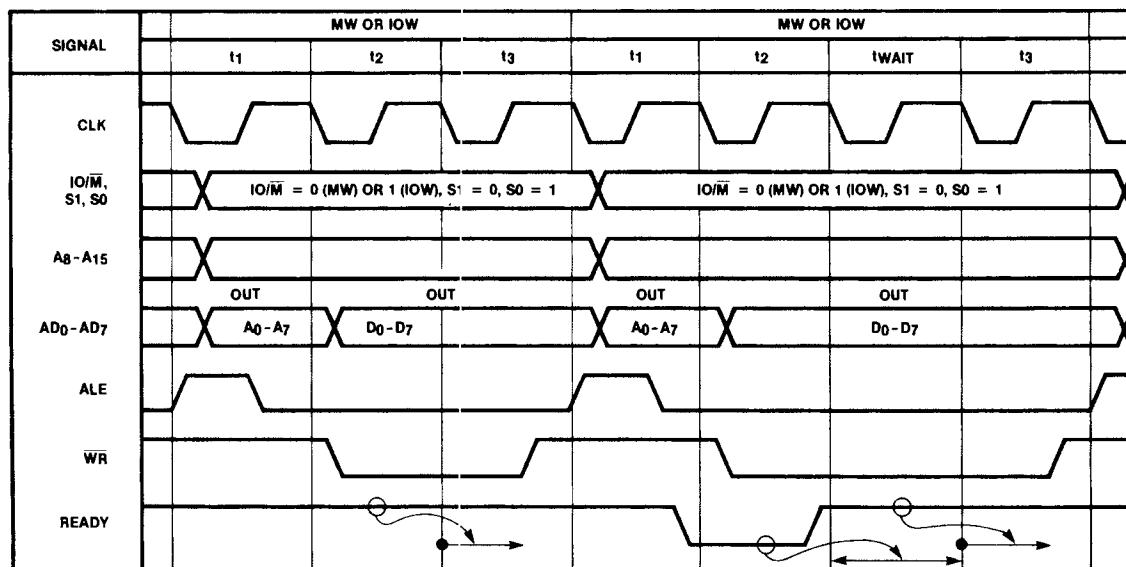

| 3-5    | PIT Programming Sequence Examples . . . . .                              | 3-8  | 4-3    | Typical CPU Instruction Cycle . . . . .                      | 4-5  |

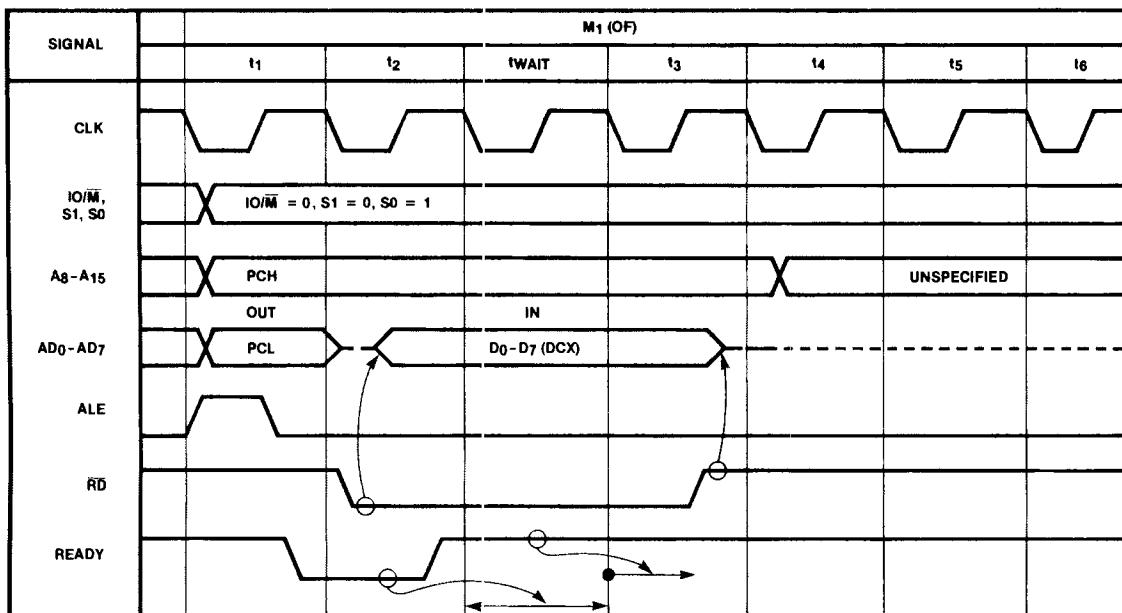

| 3-6    | PIT Counter Register Latch Control Word Format . . . . .                 | 3-10 | 4-4    | Opcode Fetch Machine Cycle (No Wait) . . . . .               | 4-5  |

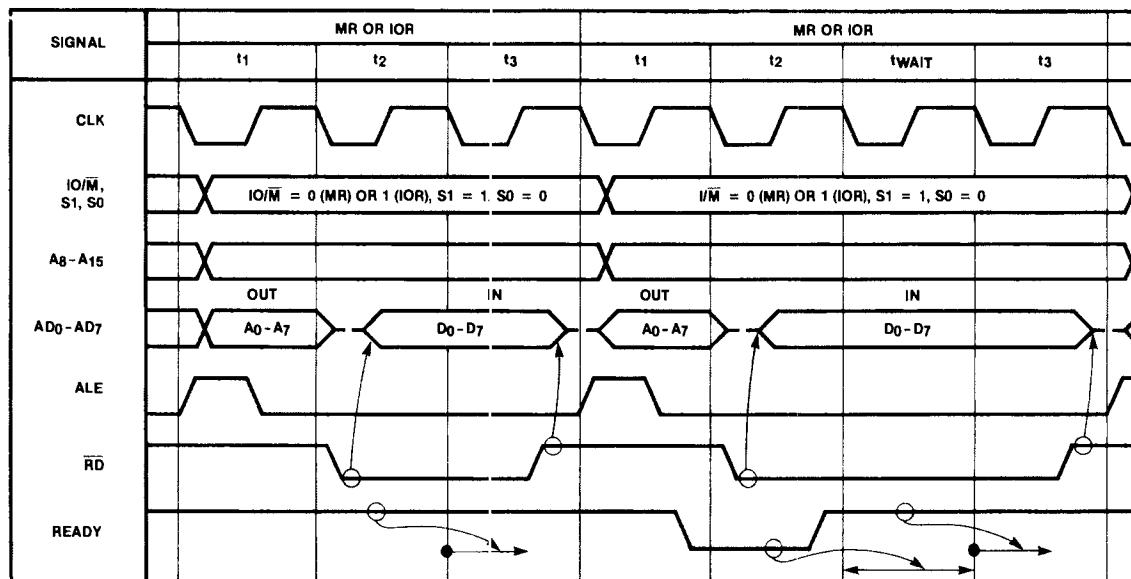

| 3-7    | PIC Interrupt Routine Addresses . . . . .                                | 3-13 | 4-5    | Opcode Fetch Machine Cycle (With Wait) . . . . .             | 4-6  |

| 3-8    | PIC Initialization Command Word Formats . . . . .                        | 3-14 | 4-6    | Memory Read (or I/O Read) Machine Cycle . . . . .            | 4-6  |

| 3-9    | PIC Operation Control Word Formats . . . . .                             | 3-15 | 4-7    | Memory Write (or I/O Write) Machine Cycles . . . . .         | 4-7  |

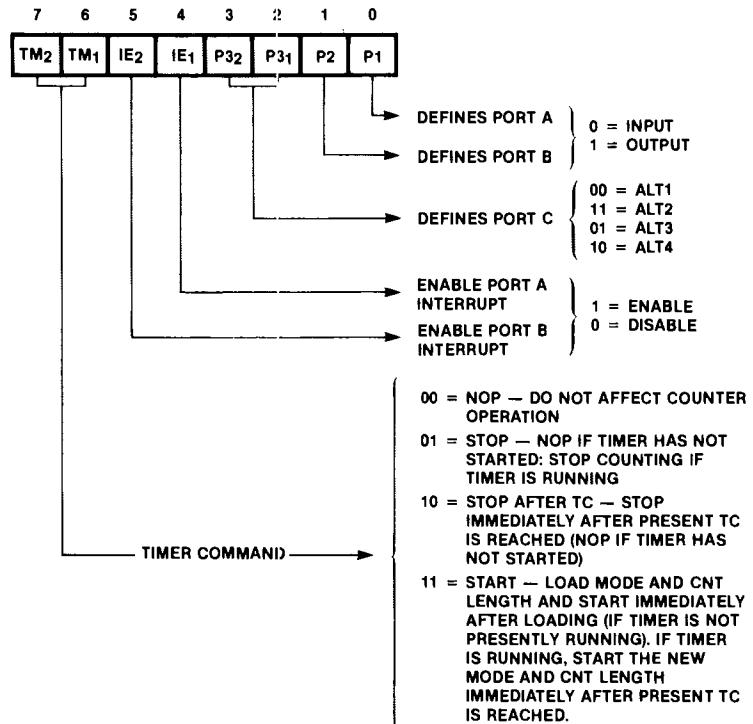

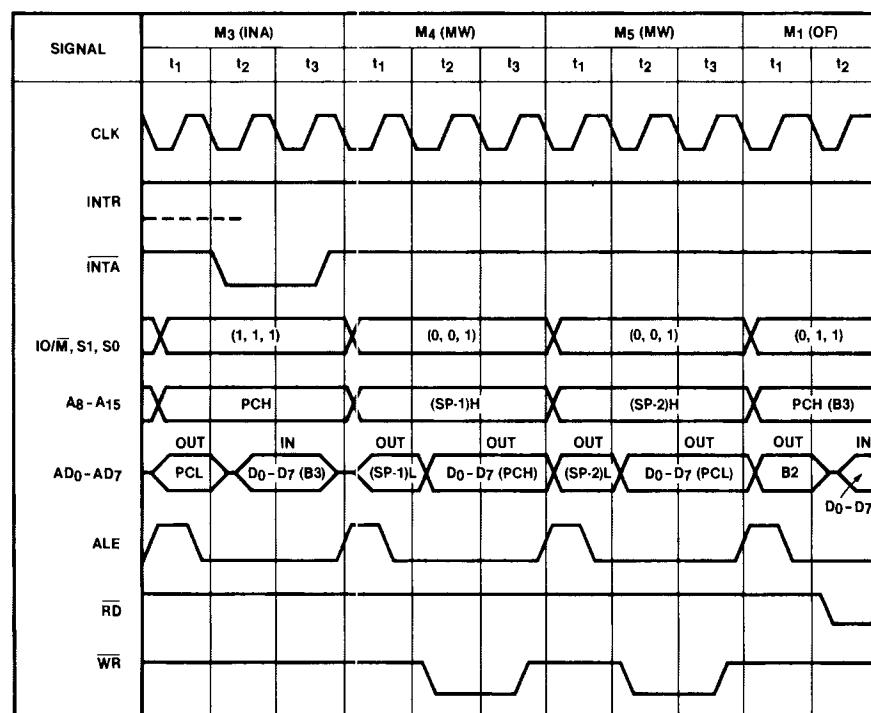

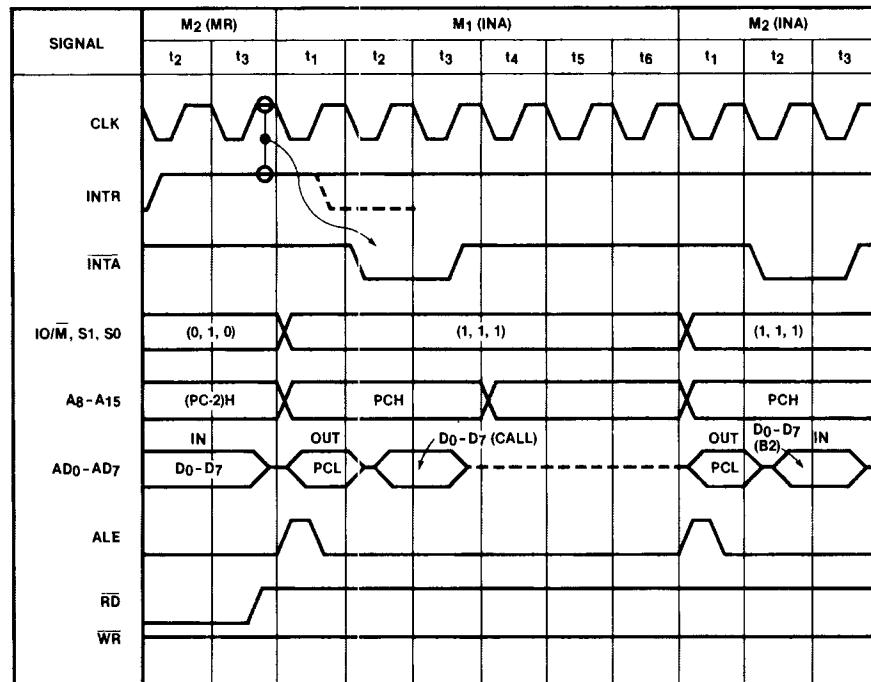

| 3-10   | Command Register Format . . . . .                                        | 3-20 | 4-8    | Interrupt Acknowledge Machine Cycles . . . . .               | 4-8  |

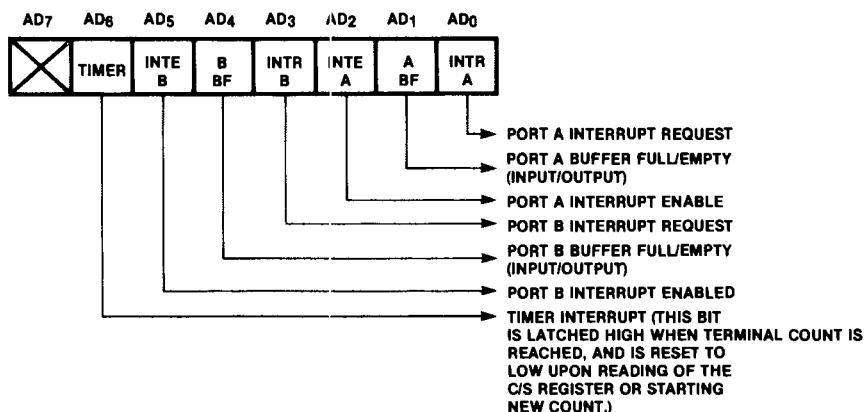

| 3-11   | Status Register Format . . . . .                                         | 3-21 | 4-9    | Address Bus and Buffers . . . . .                            | 4-9  |

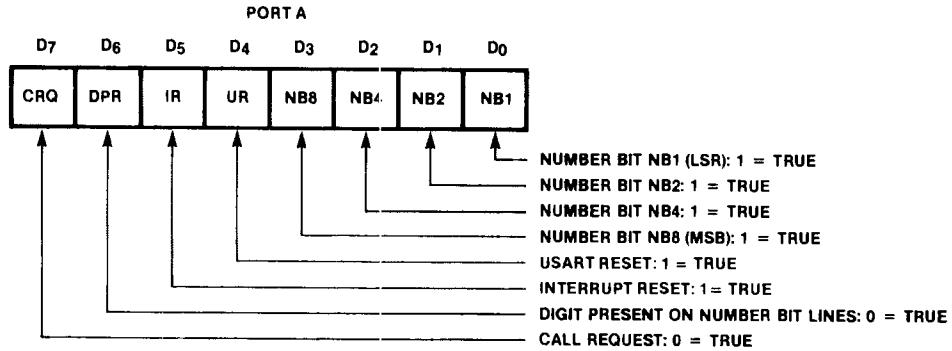

| 3-12   | PPI Port A Bit Definitions . . . . .                                     | 3-22 | 4-10   | Data Bus and Buffers . . . . .                               | 4-9  |

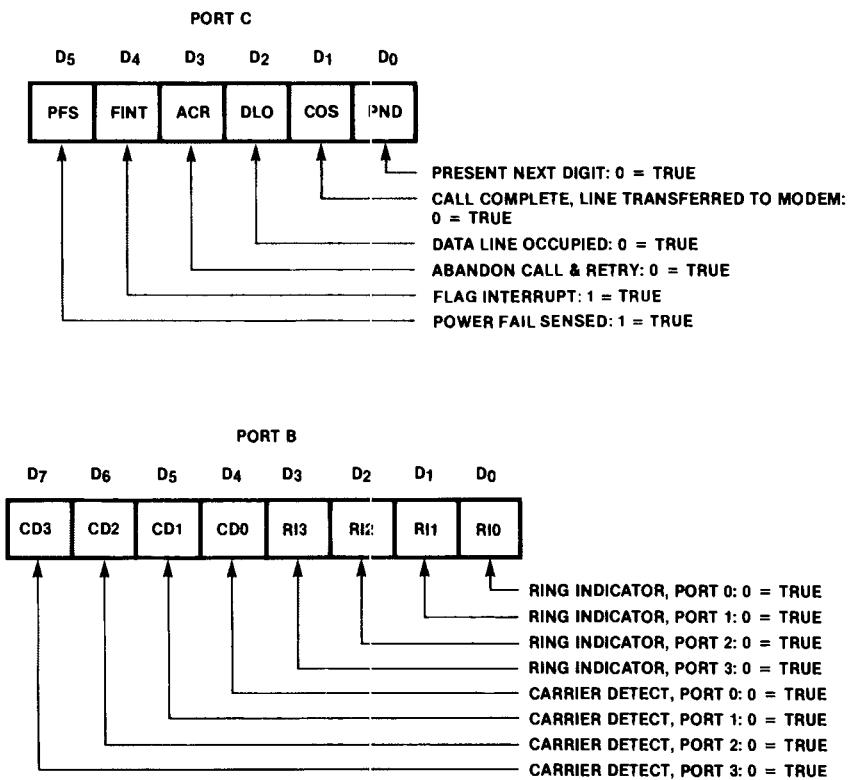

| 3-13   | Port B and C Bit Definitions . . . . .                                   | 3-23 | 4-11   | Command and Acknowledge Logic . . . . .                      | 4-10 |

| 3-14   | Timer Format . . . . .                                                   | 3-23 | 4-12   | Advance Command Signals . . . . .                            | 4-10 |

| 3-15   | Synchronous Mode Instruction Word Format . . . . .                       | 3-25 |        |                                                              |      |

## 1-1. INTRODUCTION

The iSBC 544 Intelligent Communications Controller is a member of a complete line of Intel iSBC 80 system components. The iSBC 544 operates as an intelligent slave on the system, providing an expansion of system serial communications capability, including four fully programmable synchronous and asynchronous serial I/O channels with RS232C buffering. As an intelligent slave, the iSBC 544 employs its own 8085A CPU to handle all on-board processing. Baud rates, data formats, and interrupt priorities are individually software selectable for each channel. The iSBC 544 also includes 10 lines of buffered parallel I/O interface which provides compatibility with a Bell 801 Automatic Calling Unit.

The iSBC 544 is a self-contained communications processor that incorporates an 8085A CPU (for on board processing only), up to 16K bytes of dynamic RAM, 8K bytes of PROM, and the aforementioned I/O interface. The intelligent slave concept allows the iSBC 544 to unburden a system CPU by performing all communications related peripheral tasks without constant interruption of the CPU. This concept allows for maximum I/O throughput on the system, with a minimum amount of impact on the system bus. The iSBC 544 accepts commands from the master CPU, performs the necessary functions to complete the peripheral operation, interrupts the master CPU on completion and allows the transfer of data into or out of on-board memory.

The iSBC 544 is also capable of operating as a single board communications computer. In this mode, it can control a number of iSBC 534 Communication Expansion boards or other memory and I/O expansion boards. A list of the bus limitations of the iSBC 544 used in this mode can be found in Chapter 3.

## 1-2. DESCRIPTION

The iSBC 544 (figure 1-1) is designed to be plugged into a standard iSBC 604/614 Modular Backplane and Cardcage to interface directly with an Intel iSBC Single Board Computer or used with an Intel Microcomputer Development System. The iSBC 544 provides four serial I/O ports, one parallel I/O port, seven programmable timers, and eight interrupt inputs with programmable priority. Also provided is a dedicated on-board processor consisting of an 8085A CPU and memory.

## 1-3. SERIAL I/O PORTS

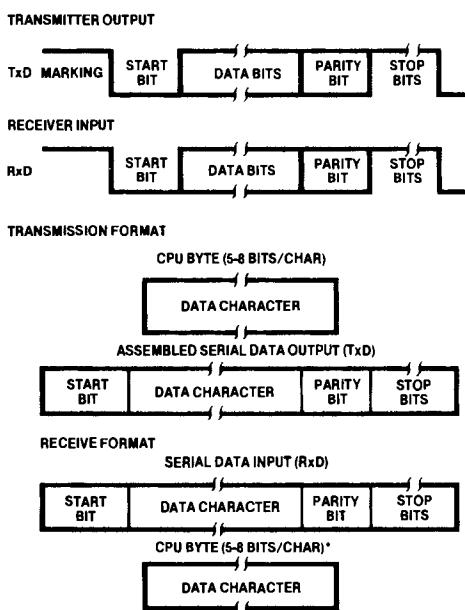

Each of the four serial I/O ports is fully RS232C plug compatible and is controlled and interfaced by an Intel 8251A USART (Universal Synchronous/Asynchronous Receiver/Transmitter) chip. Each USART is individually programmable for operation in most synchronous or asynchronous serial data transmission formats (including IBM Bi-Sync).

Figure 1-1. iSBC 544 Intelligent Communications Controller Board

In the synchronous mode the following are programmable:

- a. Character length,

- b. Sync character (or characters), and

- c. Parity.

In the asynchronous mode the following are programmable:

- a. Character length,

- b. Baud rate factor (clock divide ratios of 1, 16, or 64),

- c. Number of Stop bits, and

- d. Parity.

In both the synchronous and asynchronous modes, each serial I/O port features half- or full-duplex, double-buffered transmit and receive capability. In addition, USART error detection circuits can check for parity, overrun, and framing errors. The USART transmit and receive clock rates are separately derived from one of five independently programmable Baud rate/time generators.

#### 1-4. PARALLEL I/O PORT

The parallel I/O port has 10 buffered I/O lines controlled by an Intel 8155 Programmable Interface (PPI) chip. The parallel I/O port is directly compatible with an Automatic Calling Unit (ACU) such as the Bell Model 801, or equivalent, and can also be used for auxiliary functions. All signals are RS232C compatible, and the interface cable signal assignments meet RS366 specifications.

If the system application does not require an interface to an ACU, the parallel I/O port can be used for any general purpose or auxiliary parallel interface that is RS232C compatible.

#### 1-5. PROGRAMMABLE TIMERS

One of the primary features of the iSBC 544 is flexible clock programming. The iSBC 544 has two Intel 8253 Programmable Interval Timer (PIT) chips that provide a total of six separate time/rate generators. All six are independently software-programmable, and can generate different Baud rate clock signals for each USART chip.

Four of the timers (BDG0-BDG3) are used as Baud rate generators; the fifth timer can be used as an auxiliary transmit or receive clock, and the sixth timer can be used to generate an interrupt.

In addition to the timers on the 8253 PITs, the iSBC 544 has a 14-bit timer located on the 8155 PPI which can be used for miscellaneous functions.

#### 1-6. INTERRUPT FUNCTIONS

The iSBC 544 has the following interrupt sources:

- a. Eight serial I/O interrupts serviced by an 8259 Programmable Interrupt Controller (PIC).

- b. Flag Interrupt

- c. Carrier Detect and Ring Indicator Interrupts

- d. Multibus interrupts

- e. Timer Interrupts

The 8259 PIC has eight input interrupt request lines. The PIC treats each true input signal condition as an interrupt request. After resolving the interrupt priority, the PIC issues a single interrupt request to the on-board 8085A CPU. The interrupt priorities of the PIC chip are independently programmable under software control. The programmable interrupt priority modes are:

- a. Fully Nested Priority. Each interrupt request has a fixed priority: input 0 is highest, input 7 is lowest.

- b. Auto-Rotating Priority. Each interrupt request has equal priority. Each level, after receiving service, becomes the lowest priority level until the next interrupt occurs.

- c. Specific Priority. Software assigns lowest priority. Priority of all other levels is in numerical sequence based on lowest priority.

The Flag Interrupt allows any bus master to interrupt the iSBC 544 by writing into the base address of RAM memory. The flag interrupt is cleared when the on-board processor reads the base address. This flag provides a unique interrupt to each iSBC 544 in the system.

The Carrier Detect and Ring Indicator Interrupts allow the iSBC 544 to monitor the serial I/O ports and detect the loss of a carrier signal or the ringing of a telephone line respectively. These interrupts are detected by the on-board 8085A CPU, and available for interrogation through the 8155 PPI.

The iSBC 544 can generate an interrupt on the Multibus, and also receive an interrupt from the bus.

#### 1-7. 8085A CPU

The 8085A CPU, which is the heart of the iSBC 544, performs on-board processing functions and generates the addresses and control signals required to access memory and I/O devices. The 8085A contains six 8-bit general purpose registers and an accumulator. The six general purpose registers may be addressed individually or in pairs, providing both single and double precision operations.

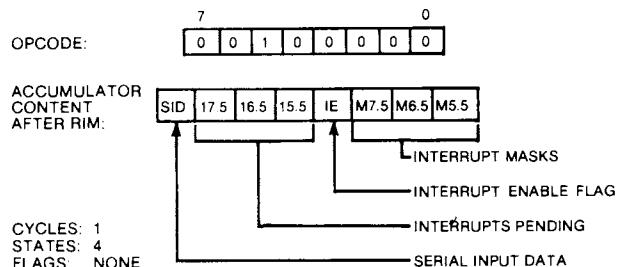

The 8085A has 5 prioritized interrupt inputs (TRAP, RST 7.5, RST 6.5, RST 5.5, and INTR) which generate unique memory addresses for interrupt handling routines. All interrupt inputs with the exception of TRAP may be masked via software.

## 1-8. PROM CONFIGURATION

The ROM/PROM on the iSBC 544 consists of either 4K or 8K bytes. Two sockets are provided for user installation of the PROM chips. Jumpers are provided for accommodation of different types of chips (Intel 2716, or 2732E PROMs and 2316, or 2332 ROMs). Address block 0000-1FFF is reserved for PROM use only.

## 1-9. RAM CONFIGURATION

The iSBC 544 includes 16K of dynamic RAM implemented with eight Intel 2117 chips and an Intel 8202 Dynamic RAM Controller. Dual-port control logic allows the RAM to be accessed by either the on-board 8085A, or by another bus master. The RAM decode logic allows for extended Multibus addressing

of up to 20 address lines. This allows bus masters with 20-bit addressing capability to partition the iSBC 544 into 16K segments in a 1-mega-byte address space. The on-board 8085A CPU, however, has only a 16-bit address capability, and limits the on-board RAM to a 64K address space.

The iSBC 544 also has 256 bytes of static RAM located on the Intel 8155 PPI. This memory is only accessible to the on-board 8085A CPU. The address block for the static RAM is 7F00-7FFF.

## 1-10. EQUIPMENT SUPPLIED

The following are supplied with the iSBC 544 Intelligent Communications Controller:

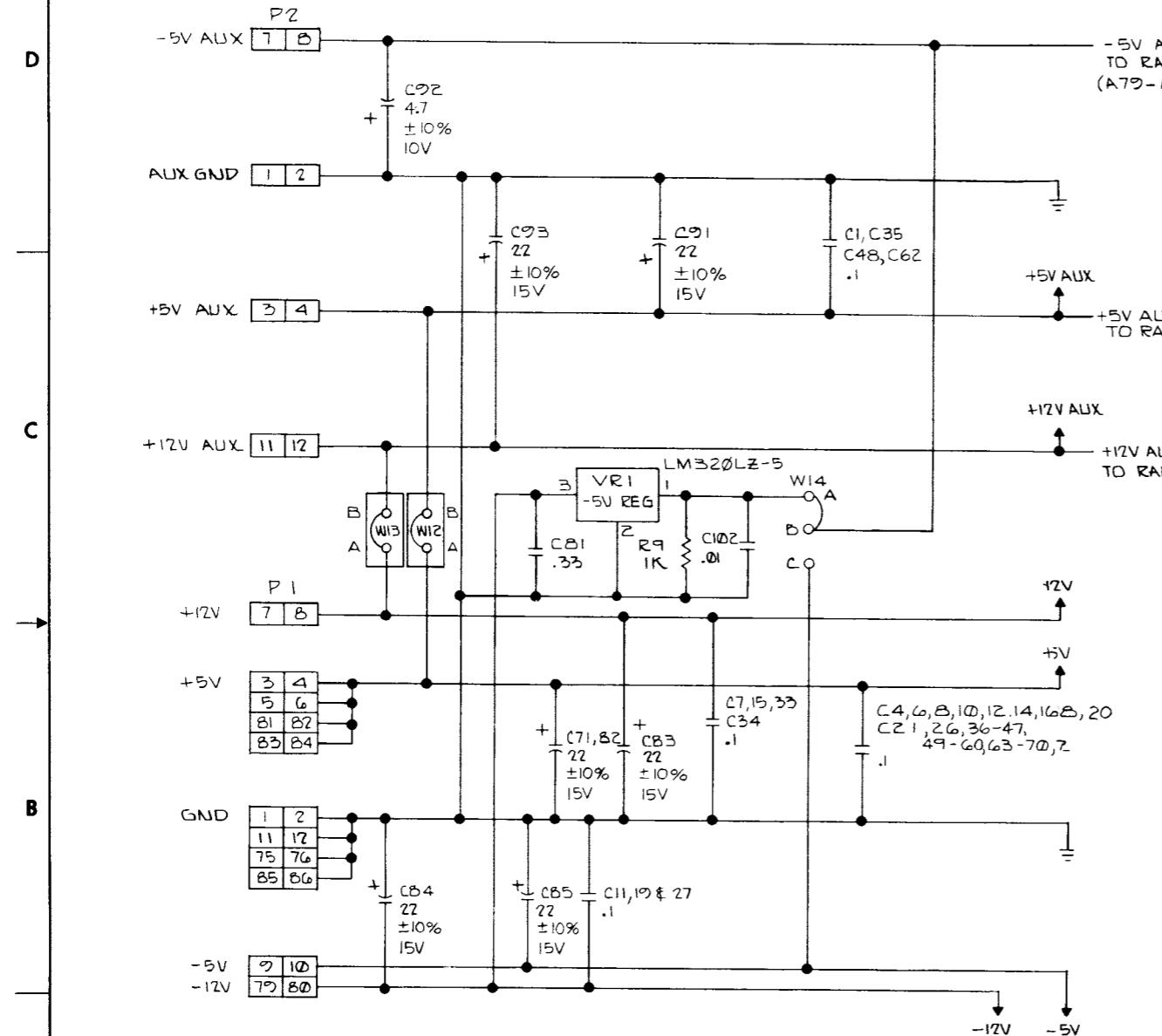

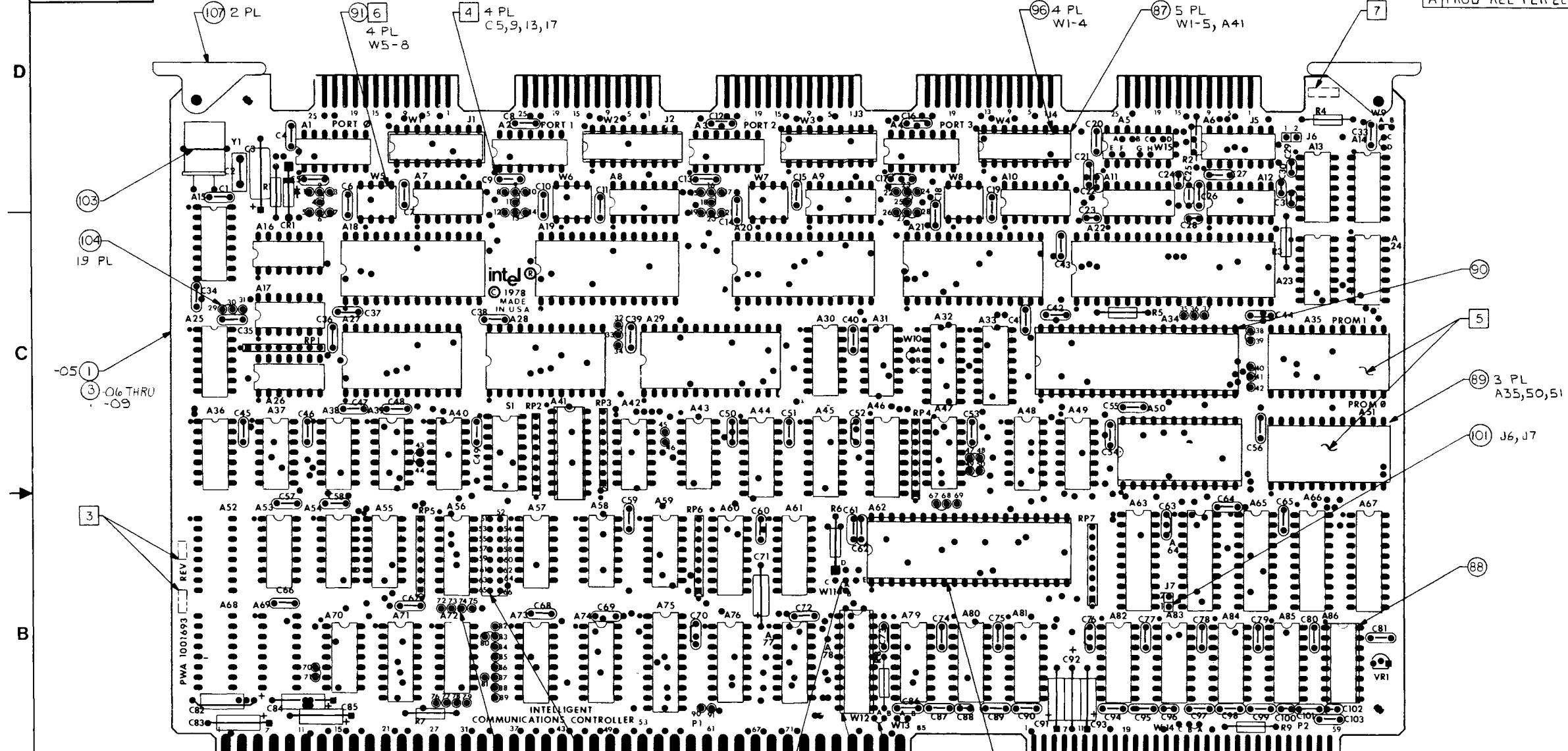

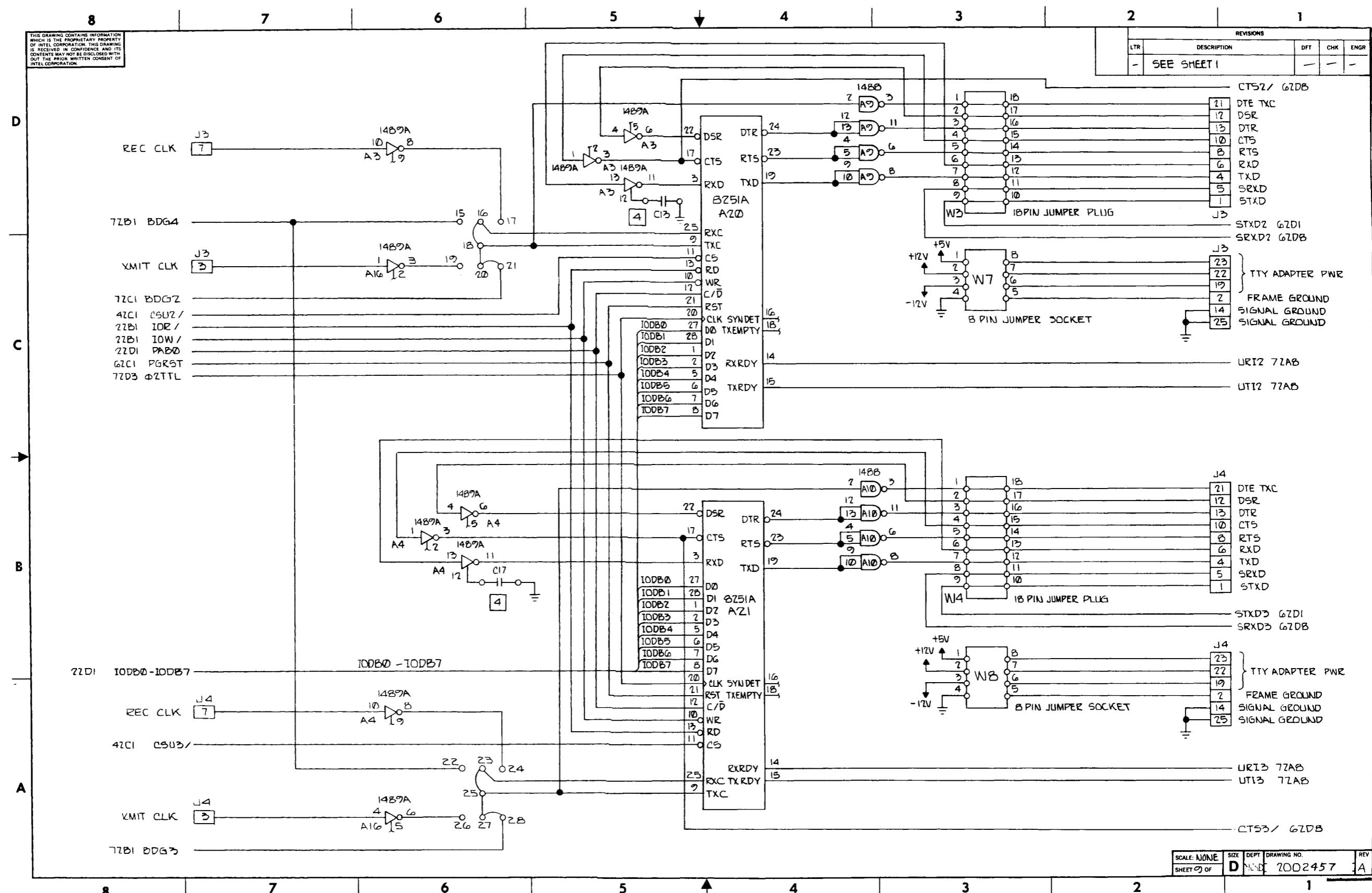

- a. Schematic Drawing, dwg. no. 2001695

- b. Assembly Drawing, dwg. no. 1001693

## 1-11. SPECIFICATIONS

Specifications for the iSBC 544 Intelligent Communications Controller are provided in table 1-1.

Table 1-1. Specifications

|                                 |                                                                                                                                                                                                                                                                        |

|---------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>8085A CPU</b>                |                                                                                                                                                                                                                                                                        |

| <b>WORD SIZE</b>                |                                                                                                                                                                                                                                                                        |

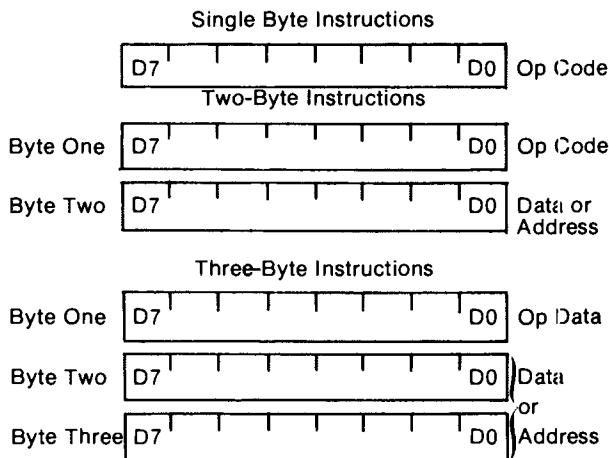

| Instruction:                    | 8, 16, or 24 bits                                                                                                                                                                                                                                                      |

| Data:                           | 8 bits                                                                                                                                                                                                                                                                 |

| <b>CYCLE TIME:</b>              |                                                                                                                                                                                                                                                                        |

|                                 | 1.45 $\mu$ sec $\pm$ 0.1% for fastest executable instruction; i.e., four clock cycles.                                                                                                                                                                                 |

| <b>MEMORY CAPACITY</b>          |                                                                                                                                                                                                                                                                        |

| On-Board ROM/PROM               | 4K or 8K of user installed ROM/PROM.                                                                                                                                                                                                                                   |

| On-Board RAM (Dynamic)          | 16K of RAM. Integrity maintained during power failure with user-furnished batteries. (optional)                                                                                                                                                                        |

| On-Board RAM (Static)           | 256 bytes of RAM:                                                                                                                                                                                                                                                      |

| <b>MEMORY ADDRESSING:</b>       |                                                                                                                                                                                                                                                                        |

| On-Board ROM/PROM               | 0000-1FFF                                                                                                                                                                                                                                                              |

| On-Board Static RAM             | 7F00-7FFF                                                                                                                                                                                                                                                              |

| On-Board RAM                    | 16K: 8000-BFFF                                                                                                                                                                                                                                                         |

| On-Board RAM<br>(System Access) | Jumpers allow board to act as slave memory for other bus masters. 16 or 20 bit addressing can be accommodated. Boundaries may be set on any 4K increment 00000-FF000, which is switch selectable. 4K, 8K, or 16K can be made available to the bus by switch selection. |

| <b>CPU RAM ACCESS TIME:</b>     |                                                                                                                                                                                                                                                                        |

|                                 | 450 nsec min, and 1100 nsec + off-board command duration max. CPU has priority over bus master access, however CPU request cannot abort bus master access in progress.                                                                                                 |

Table 1-1. Specifications (Cont'd.)

| MINIMUM WAIT STATE<br>CONSIDERATIONS | Type | On-Board Request |         | Off-Board Request<br>(Master Mode) |         |

|--------------------------------------|------|------------------|---------|------------------------------------|---------|

|                                      |      | Normal           | Refresh | Normal                             | Refresh |

| I/O Read/Write                       | None | N/A              |         | N/A                                | N/A     |

| Memory Write (Dyn.)                  | 1    | 2                |         | 2                                  | 3       |

| Memory Read (Dyn.)                   | None | 1                |         | 1                                  | 2       |

| Memory Write (Stat.)                 | None | None             |         | N/A                                | N/A     |

| Memory Read (Stat.)                  | None | None             |         | N/A                                | N/A     |

Note: Dyn.=Dynamic RAM

Stat.=Static RAM or PROM

**INTERRUPTS:**

8085A CPU includes five interrupt inputs, each of which vectors the processor to the following memory location for entry point to service routine:

| Interrupt Input | Vector Address | Priority | Type         |

|-----------------|----------------|----------|--------------|

| TRAP            | 24             | 1        | Non-Maskable |

| RST 7.5         | 3C             | 2        | Maskable     |

| RST 6.5         | 34             | 3        | Maskable     |

| RST 5.5         | 2C             | 4        | Maskable     |

| INTR            | Note           | 5        | Maskable     |

Note: INTR input provided by 8259 PIC. See table 3-27 for vector addresses.

**SERIAL COMMUNICATIONS**

Synchronous: 5-, 6-, 7-, or 8-bit characters. Internal; 1 or 2 sync characters. Automatic sync insertion, parity and overrun error detection.

Asynchronous: 5-, 6-, 7-, or 8-bit characters. Break character generation and detection, 1, 1½, or 2 stop bits. False start bit detection, parity, overrun and framing error detection.

Sample Baud Rate:

| Frequency <sup>1</sup><br>(kHz, Software Selectable) | Baud Rate (Hz) <sup>2</sup> |              |

|------------------------------------------------------|-----------------------------|--------------|

|                                                      | Synchronous                 | Asynchronous |

|                                                      | ÷16                         | ÷64          |

| 153.6                                                | —                           | 9600 2400    |

| 76.8                                                 | —                           | 4800 1200    |

| 38.4                                                 | 38400                       | 2400 600     |

| 19.2                                                 | 19200                       | 1200 300     |

| 9.6                                                  | 9600                        | 600 150      |

| 4.8                                                  | 4800                        | 300 75       |

| 6.98                                                 | 6980                        | — 110        |

Notes:

1. Frequency selected by I/O writes of appropriate 16-bit frequency factor to counter/timer Register.

2. Baud rates shown here are only a sample subset of possible software-programmable rates available. Any frequency from 18.75 Hz to 614.4 kHz may be generated utilizing on-board crystal oscillator and 16-bit Programmable Interval Timer (used here as frequency divider).

**INTERVAL TIMER AND BAUD RATE GENERATOR**

Input Frequency: On board 1.2288 MHz .1% crystal; 0.814 microsecond period, nominal or 1.8432 MHz ±.1% crystal; 0.542 microsecond period, nominal.

Table 1-1. Specifications (Cont'd.)

| Output Frequencies:<br>(at 1.2288 MHz) | Function                           | Single Timer   |           | Dual Timers<br>(Two Timers Cascaded) |               |

|----------------------------------------|------------------------------------|----------------|-----------|--------------------------------------|---------------|

|                                        |                                    | Min            | Max       | Min                                  | Max           |

|                                        | Real-Time<br>Interrupt<br>Interval | 1.63 $\mu$ sec | 53.3 msec | 3.26 $\mu$ sec                       | 58.25 minutes |

| Rate<br>Generator<br>(Frequency)       |                                    | 18.75 Hz       | 614.4 kHz | 0.00029 Hz                           | 307.2 kHz     |

**INTERFACE COMPATIBILITY**

Serial I/O:

EIA Standard RS232C signals provided and supported:

|                     |                          |

|---------------------|--------------------------|

| Carrier Detect      | Receive Data             |

| Clear to Send       | Ring Indicator           |

| Data Set Ready      | Secondary Receive Data*  |

| Data Terminal Ready | Secondary Transmit Data* |

| Request to Send     | Transmit Clock           |

| Receive Clock       | Transmit Data            |

| DTE Transmit        |                          |

\* Optional if parallel port not used as ACU.

Parallel I/O:

4 input lines and 6 output lines; all signals compatible with EIA Standard RS232C. Directly compatible with Bell Model 801 Automatic Calling Unit.

System Bus:

Compatible with Intel iSBC 80 Multibus.

**I/O ADDRESSING:**

All communication to parallel and serial I/O ports, timers, and the interrupt controller is via read and write commands from the on-board 8085A CPU. Refer to table 3-2 for specific addresses.

**COMPATIBLE CONNECTORS/CABLE:**

Refer to table 2-2 for compatible connector details.

**POWER REQUIREMENTS:**

|                         | 1                        | 2                        | 3                     | 4                     |

|-------------------------|--------------------------|--------------------------|-----------------------|-----------------------|

| $V_{CC} = +5V \pm 5\%$  | $I_{CC} = 3.4$ max.      | $I_{CC} = 3.3A$ max.     | $I_{CC} = 390mA$ max. | $I_{CC} = 390mA$ max. |

| $V_{DD} = +12V \pm 5\%$ | $I_{DD} = 350mA$ max.    | $I_{DD} = 350$ max.      | $I_{DD} = 176mA$ max. | $I_{DD} = 20mA$ max.  |

| $V_{BB} = -5V \pm 5\%$  | $I_{BB} = \text{Note 5}$ | $I_{BB} = \text{Note 5}$ | $I_{BB} = 5mA$ max.   | $I_{BB} = 5mA$ max.   |

| $V_{AA} = -12V \pm 5\%$ | $I_{AA} = 200mA$ max.    | $I_{AA} = 200mA$ max.    |                       |                       |

Notes:

- Assuming two 2716 PROMs installed

- No PROMs installed

- For operational RAM only, for AUX power supply rating.

- For RAM refresh only. Used for battery backup requirements. No RAM accessed.

- $V_{BB}$  is normally derived on board from  $V_{AA}$ . If  $V_{BB}$  supplied from bus, max requirement is 5mA.

**ENVIRONMENTAL REQUIREMENTS**

Operating Temperature: 0° to 55° (32° to 131°F).

Relative Humidity: To 90% without condensation.

**PHYSICAL CHARACTERISTICS**

|            |                          |

|------------|--------------------------|

| Width:     | 30.48 cm (12.00 inches). |

| Depth:     | 17.15 cm (6.75 inches).  |

| Thickness: | 1.27 cm (0.50 inch).     |

| Weight:    | 397 gm (14 ounces).      |

## CHAPTER 2 PREPARATION FOR USE

### 2-1. INTRODUCTION

This chapter provides information for preparing the iSBC 544 Intelligent Communications Controller for use in the user-defined environment. This information includes unpacking and inspection; installation considerations; optional component installation; jumper configurations; multibus configuration; data set conversion; power fail/memory protect configuration; I/O cabling; and board installation.

### 2-2. UNPACKING AND INSPECTION

Inspect the shipping carton immediately upon receipt for evidence of mishandling during transit. If the shipping carton is severely damaged or waterstained, request that the carrier's agent is present when the carton is opened. If the carriers agent is not present when the carton is opened, and the contents of the carton are damaged, keep the carton and packing material for the agent's inspection.

For repairs to a product damaged in shipment, contact the Intel Technical Support Center (see paragraph 5-4) to obtain a Return Authorization Number and further instructions. A purchase order will be required to complete the repair. A copy of the purchase order should be submitted to the carrier with your claim.

It is suggested that salvageable shipping cartons and packing material be saved for future use in the event the product must be shipped.

### 2-3. INSTALLATION CONSIDERATIONS

The iSBC 544 Intelligent Communications Controller is designed for use as an "intelligent slave". It can be used any time the user desires to maximize I/O throughput with a minimum amount of impact on the system bus. The iSBC 544 is able to do this, because of its architecture which consists of a dedicated on-board 8085A CPU, dedicated on-board memory, and a variety of peripheral chips which perform such functions as format control, code conversions, data link control, error checking, and buffer management.

Important criteria for installing and interfacing the iSBC 544 in the above environment is presented in the following paragraphs.

### 2-4. USER FURNISHED COMPONENTS

Because the iSBC 544 can be used in a variety of applications, the user must purchase and install only those components which satisfy his particular needs. A list of components required to configure the iSBC 544 can be found in table 2-1. Table 2-2 is a list of the types and vendors of those connectors listed in table 2-1.

### 2-5. POWER REQUIREMENTS

The iSBC 544 requires +5V, +12V, and -12V power supply inputs. The currents required from these supplies are listed in table 1-1.

Table 2-1. User Furnished and Installed Components

| ITEM<br>No. | ITEM                         | DESCRIPTION                                                                  | USE                                                                                                                             |

|-------------|------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|

| 1           | iSBC 604                     | Modular Backplane and Cardcage. Includes four slots with bus terminators.    | Provides power input pins and Multibus signal interface between iSBC 544 and three additional boards in a multiple board system |

| 2           | iSBC 614                     | Modular Backplane and Cardcage. Includes four slots without bus terminators. | Provides four-board extensions of iSBC 604                                                                                      |

| 3           | Connector<br>(mates with P1) | See Multibus Connector details in table 2-2.                                 | Power inputs and Multibus signal interface. Not required if iSBC 544 installed in an iSBC 604/614.                              |

Table 2-1. User Furnished and Installed Components (Cont'd.)

| ITEM No. | ITEM                                     | DESCRIPTION                                     | USE                                                                                      |

|----------|------------------------------------------|-------------------------------------------------|------------------------------------------------------------------------------------------|

| 4        | Connector (mates with P2)                | See Auxiliary connector details in table 2-2.   | Auxiliary backup battery inputs and associated memory protect functions                  |

| 5        | Connector (mates with J1, J2, J3, or J4) | See Serial I/O connector details in table 2-2.  | Interfaces Serial I/O ports to Intel 8251A Programmable Communications Interface (USART) |

| 6        | Connector (mates with J5)                | See parallel I/O connector details in table 2-2 | Interface parallel I/O port to Intel 8155                                                |

| 7        | EPROM chips                              | Intel 2716 (2Kx8)<br>Intel 2732/2732A (4Kx8)    | On-board UV erasable EPROM for program development and/or dedicated program use.         |

| 8        | Capacitors                               | Four capacitors as required.                    | Rise time/noise capacitors for serial I/O port.                                          |

| 9        | Jumpers                                  | —                                               | To connect optional power to serial I/O connectors J1-J4.                                |

| 10       | DIP Header Jumper                        | —                                               | To convert data terminal interface to data set interface                                 |

Table 2-2. User Furnished Connector Details

| FUNCTION                               | NO. OF PAIRS/ PINS | CENTERS (inches) | CONNECTOR TYPE         | VENDOR                                               | VENDOR PART NO.                                                         | INTEL PART NO.        |

|----------------------------------------|--------------------|------------------|------------------------|------------------------------------------------------|-------------------------------------------------------------------------|-----------------------|

| Parallel/ Serial I/O Connector (J1-J5) | 13/26              | 0.1              | Flat Crimp             | 3M<br>AMP<br>ANSLY<br>SAE                            | 3462-0001<br>88106-1<br>609-2615<br>SD6726 Series                       | iSBC 955<br>Cable Set |

| Parallel/ Serial I/O Connector (J1-J5) | 13/26              | 0.1              | Soldered               | TI<br>AMP                                            | H312113<br>1-583485-5                                                   | N/A                   |

| Parallel/ Serial I/O Connector (J1-J5) | 13/26              | 0.1              | Wire wrap <sup>1</sup> | TI                                                   | H311113                                                                 | N/A                   |

| Multibus Connector (PI)                | 43/86              | 0.156            | Soldered <sup>1</sup>  | CDC <sup>3</sup><br>MICRO PLASTICS<br>ARCO<br>VIKING | VPB01E43D00A1<br>MP-0156-43-BW-4<br>AE443WP1<br>Less Ears<br>2VH43/1AV5 | N/A                   |

Table 2-2. User Furnished Connector Details (Cont'd.)

| FUNCTION                 | NO. OF PAIRS/ PINS | CENTERS (inches) | CONNECTOR TYPE           | VENDOR                                         | VENDOR PART NO.                              | INTEL PART NO. |

|--------------------------|--------------------|------------------|--------------------------|------------------------------------------------|----------------------------------------------|----------------|

| Multibus Connector (P1)  | 43/86              | 0.156            | Wire wrap <sup>1,2</sup> | CDC <sup>3</sup><br>CDC <sup>3</sup><br>VIKING | VFB01E43D00A1<br>VPB01E43A00A1<br>2VH43/1AV5 | MDS 985        |

| Auxiliary Connector (P2) | 30/60              | 0.1              | Soldered <sup>1</sup>    | TI<br>VIKING                                   | H312130<br>3VH30/1JN5                        | N/A            |

| Auxiliary Connector (P2) | 30/60              | 0.1              | Wirewrap <sup>1,2</sup>  | CDC <sup>3</sup><br>TI                         | VPB011B30A00A2<br>H311130                    | N/A            |

## NOTES:

1. Connector heights are not guaranteed to conform to OEM packaging equipment.

2. Wire wrap pin lengths are not guaranteed to conform to OEM packaging equipment.

3. CDC VPB01... VPB02... VPB04... etc. are identical connectors with different electroplating thicknesses or metal surfaces.

4. Connector numbering convention may not agree with board connector numbers.

**2-6. COOLING REQUIREMENTS**

The iSBC 544 dissipates 275 gram-calories/minute (1.11 BTU/minute) and adequate circulation of air must be provided to prevent a temperature rise above 55°C (131°F). The System 80 enclosures and the Intellic System include fans to provide adequate intake and exhaust of ventilating air.

**2-7. PHYSICAL DIMENSIONS**

Physical dimensions of the iSBC 544 are as follows:

- a. Width: 30.48cm (12.00 inches)

- b. Height: 17.15cm (6.75 inches)

- c. Thickness: 1.25cm (0.50 inch)

**2-8. COMPONENT INSTALLATION**

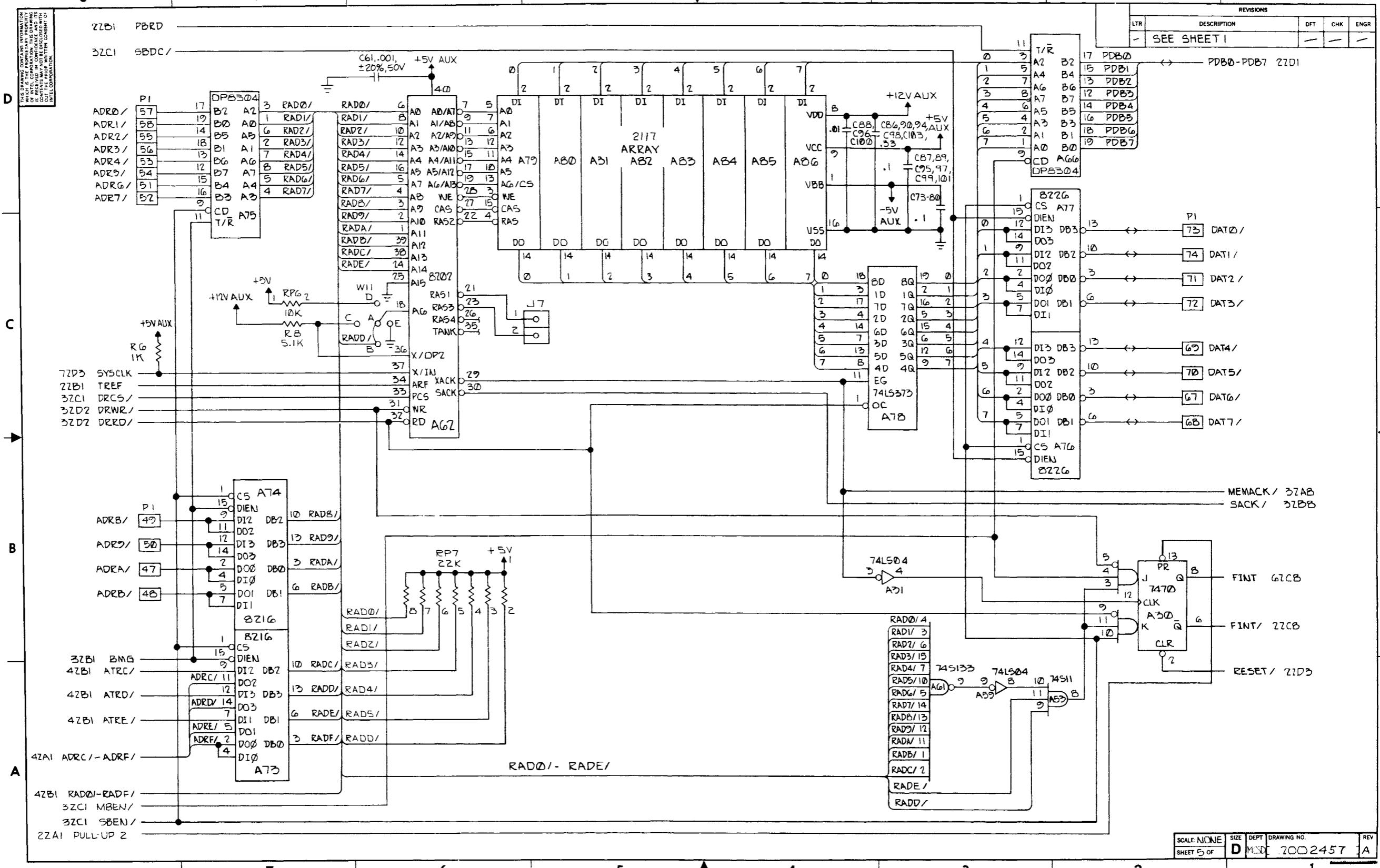

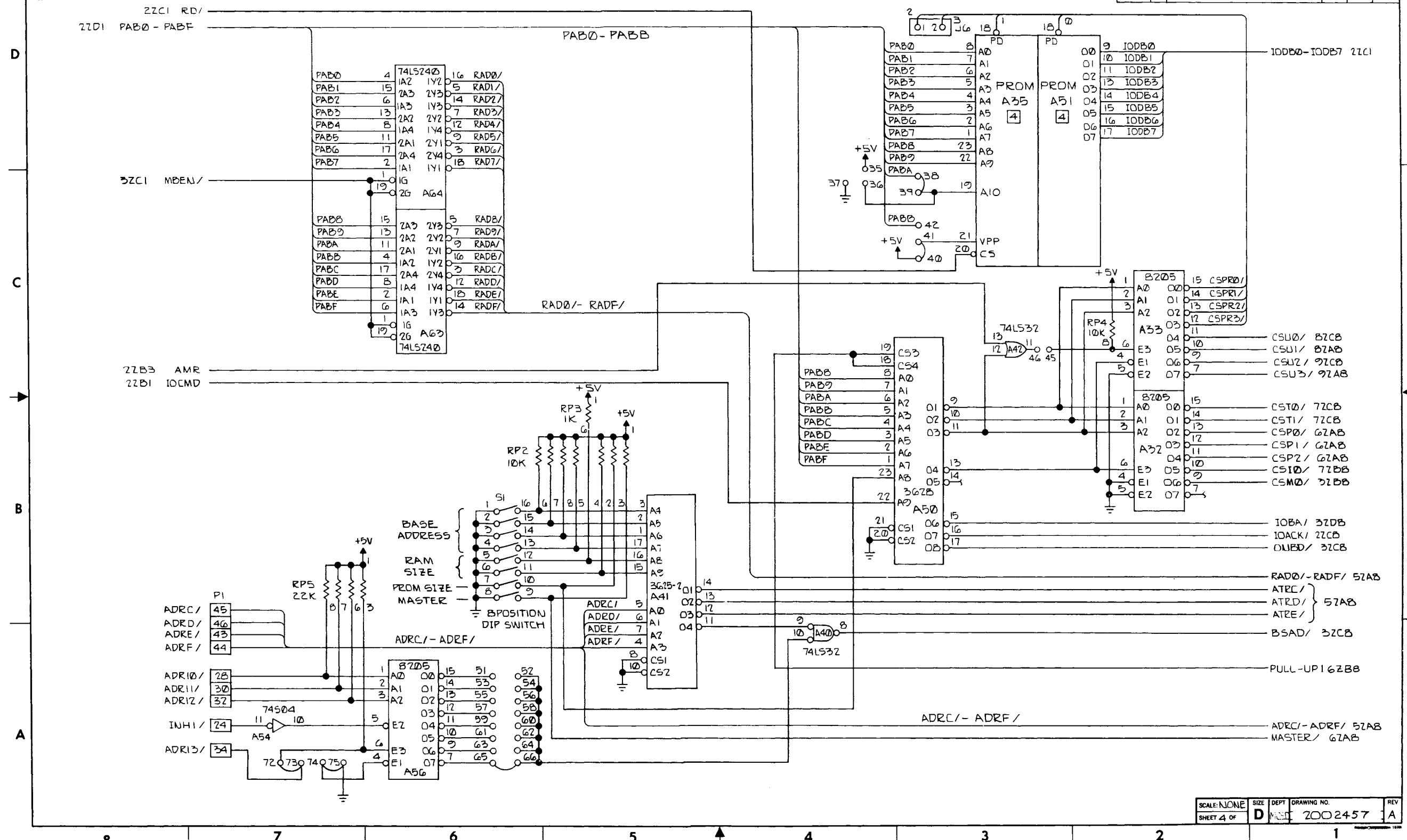

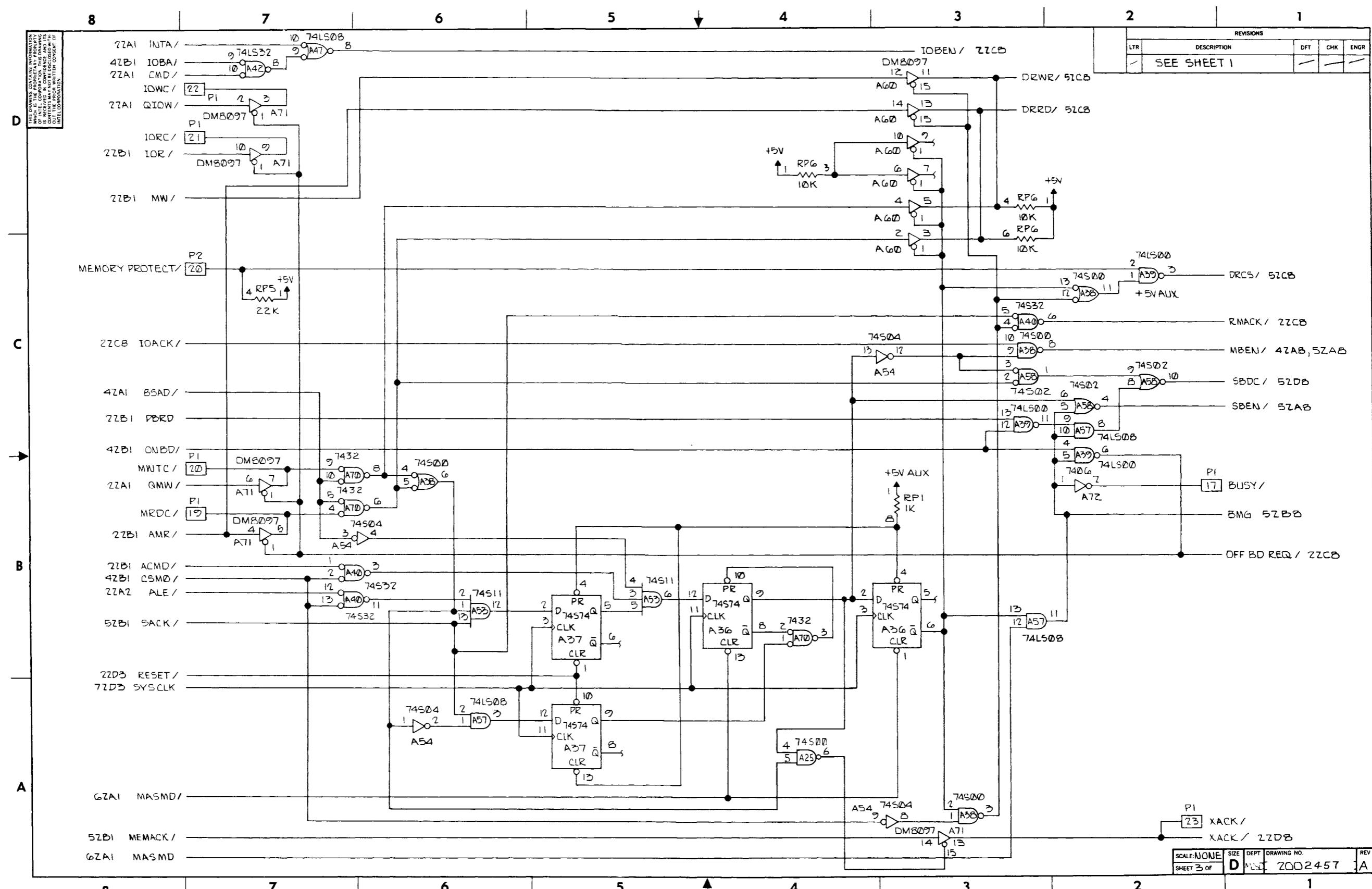

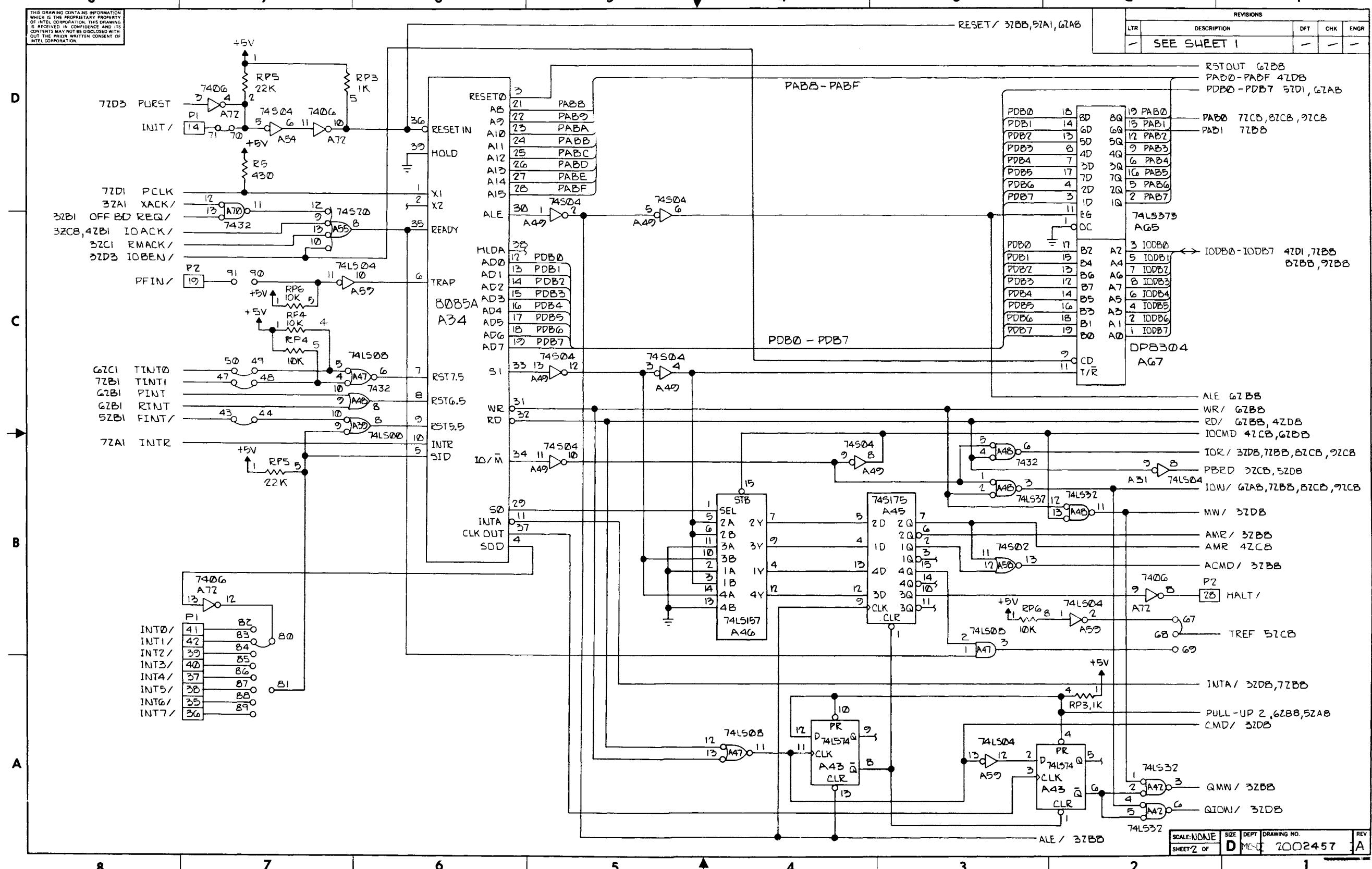

Instructions for installing the optional EPROMS, jumpers, and rise time/noise capacitors are given in the following paragraphs. When installing the optional chips; be sure to orient pin 1 of the chip adjacent to the white dot located near pin 1 of the associated IC socket. The grid location on figure 5-1 (parts location diagram) and figure 5-2 (schematic diagram) are specified for each user installed component. Because the schematic diagram consists of nine sheets, grid references to figure 5-2 consist of four alphanumeric characters. For example reference SZB3 signifies sheet 5, zone B3.

**2-9. EPROM CHIPS**

Install the EPROM chips in IC sockets A35 and A51 (refer to figure 5-1 zone C2 and figure 5-2 zone 4ZD3). Sockets A51 and A35 respectively, accommodate the low-order and high-order addresses of the EPROM chip pair. For instance if two Intel 2716 EPROM's are installed, the chip installed in IC socket A51 is assigned addresses 0000-07FF and the chip installed in IC socket A35 is assigned addresses 0800-0FFF. The default (factory connected) jumpers are configured for Intel 2716 EPROMs. If Intel 2732 EPROMs are used, A51 = 0000-0FFF and A35 = 1000-1FFF.

**2-10 RISE TIME/NOISE CAPACITORS**

Eye pads are provided so that rise time/noise capacitors may be installed as required on the individual serial I/O pins. The selection of capacitor values is at the option of the user and is normally a function of the particular environment. The location of these eye pads are as follows:

| Capacitor | FIG 5-1 | FIG 5-2 |

|-----------|---------|---------|

| C5        | D7      | 8ZD5    |

| C9        | D6      | 8ZB6    |

| C13       | D5      | 9ZD5    |

| C17       | D4      | 9ZB6    |

## 2-11 JUMPER CONFIGURATIONS

The iSBC 544 includes a variety of jumper-selectable options to allow the user to configure the board for his particular application. Table 2-3 summarizes these jumper selectable options and lists the grid reference locations of the jumpers as shown in figure 5-1 (part location diagram) and figure 5-2 (schematic diagram). The grid references for figure 5-2 are four alphanumeric characters long to denote sheet number and zone. For example grid reference 5ZB3 denotes sheet 5 zone B3.

Study table 2-3 carefully while making reference to figures 5-1 and 5-2. If the default (factory installed) jumper wiring is appropriate for a particular function, no further action is required for that function. If, however, a different configuration is required, remove the default jumper(s) and install the optional jumper(s) as specified. For most options, the information in table 2-3 is sufficient for proper configuration. Additional information, where necessary for clarity, is described in subsequent paragraphs.

## 2-12. PROM CONFIGURATION

Table 2-3 lists the jumper configurations for using 2716 PROM or 2732/2732A PROM chips and 2316 or 2332 ROM chips.

## 2-13. ON-BOARD RAM

The on-board 8085A has access to 16K of RAM starting at location 8000H. The addresses would be:

| SIZE | LOCATIONS   |

|------|-------------|

| 16K  | 8000 - BFFF |

Another bus master can access 4K, 8K, or 16K of iSBC 544 on-board RAM via the Multibus. The base address of this system accessible RAM is jumper and switch selectable as shown in table 2-3. It should be noted, that if the base address coming on the Multibus does not match the switch selectable base address, no RAM access will be allowed. This selection is performed by an Intel 3625-2 PROM located at A41 on the iSBC 544

Table 2-3 Jumper Selectable Options

| FUNCTION                        | Fig 5-1<br>GRID REF | Fig 5-2<br>GRID REF | DESCRIPTION                                                                                                                                                                                                                                                                      |

|---------------------------------|---------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PROM Configuration              | C3                  | 4ZC3                | The following jumpers accommodate one of two types of PROM chips.<br>Intel 2716/2316E - 38-39, 40-41<br>Intel 2732 - 41-42<br>Intel 2732A/2332 - 41-42, 45-46                                                                                                                    |

| PROM Size                       | C6                  | 4ZB6                | SWI Position 7 selects PROM size<br>On (0) = 8K - See Appendix D.<br>Off (1) = 4K                                                                                                                                                                                                |

| On-Board RAM<br>(System Access) | B6                  | 4ZA7                | The following describes the selection of on-board RAM by another system component.<br><br>*72-73, 74-75 - Selects lower 512K<br>73-74 - Selects upper 512K                                                                                                                       |

|                                 | B6                  | 4ZA6                | 51-52: 448-512K or 1024-1088K<br>53-54: 384-448K or 960-1024K<br>55-56: 320-384K or 832- 896K<br>57-58: 256-320K or 768- 832K      Select<br>59-60: 192-256K or 704- 768K      64K<br>61-62: 128-192K or 640- 704K<br>63-64: 64-128K or 576- 640K<br>*65-66: 0- 64K or 512- 576K |

### NOTE

Jumper selectable only on a 20 bit system.

Table 2-3 Jumper Selectable Options Continued

| FUNCTION                         | Fig 5-1<br>GRID REF     | Fig 5-2<br>GRID REF | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

|----------------------------------|-------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------|------|--|------|---------|------|---------|------|---------|------|-------------------------|----------------|----------|-----|--|-----|----|-----|----|-----|-----|-----|----|

|                                  | C6                      | 4ZB6                | <p>SW1 - Positions 1-4 select base address of the 4K, 8K, or 16K of RAM that is accessible by the system. (0=ON, 1=OFF)</p> <p>For example:</p> <table> <thead> <tr> <th>Switch Setting</th> <th>Base Address</th> </tr> </thead> <tbody> <tr> <td>4321</td> <td></td> </tr> <tr> <td>0001</td> <td>= 1000H</td> </tr> <tr> <td>0010</td> <td>= 2000H</td> </tr> <tr> <td>0100</td> <td>= 4000H</td> </tr> <tr> <td>1101</td> <td>= D000H (4K or 8K only)</td> </tr> </tbody> </table> <p>SW1- Positions 5-6 select RAM size as follows:</p> <table> <thead> <tr> <th>Switch Setting</th> <th>RAM Size</th> </tr> </thead> <tbody> <tr> <td>6 5</td> <td></td> </tr> <tr> <td>0 0</td> <td>4K</td> </tr> <tr> <td>0 1</td> <td>8K</td> </tr> <tr> <td>1 0</td> <td>16K</td> </tr> <tr> <td>1 1</td> <td>NA</td> </tr> </tbody> </table> <p><b>Note</b><br/>If the base address you select does not allow for the RAM size you have selected, you will not be able to access RAM at all. This allows for the case where the iSBC 544 RAM is not used by the bus.</p> | Switch Setting | Base Address | 4321 |  | 0001 | = 1000H | 0010 | = 2000H | 0100 | = 4000H | 1101 | = D000H (4K or 8K only) | Switch Setting | RAM Size | 6 5 |  | 0 0 | 4K | 0 1 | 8K | 1 0 | 16K | 1 1 | NA |

| Switch Setting                   | Base Address            |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 4321                             |                         |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 0001                             | = 1000H                 |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 0010                             | = 2000H                 |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 0100                             | = 4000H                 |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 1101                             | = D000H (4K or 8K only) |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| Switch Setting                   | RAM Size                |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 6 5                              |                         |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 0 0                              | 4K                      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 0 1                              | 8K                      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

| 1 0                              | 16K                     |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |

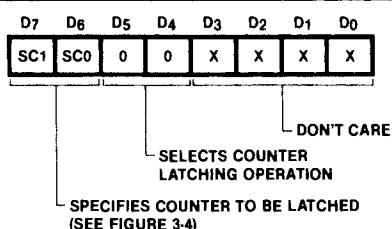

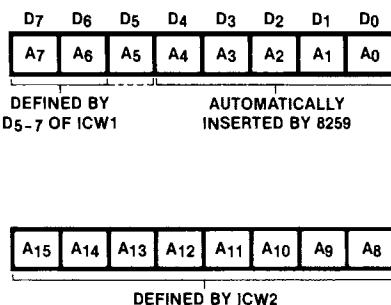

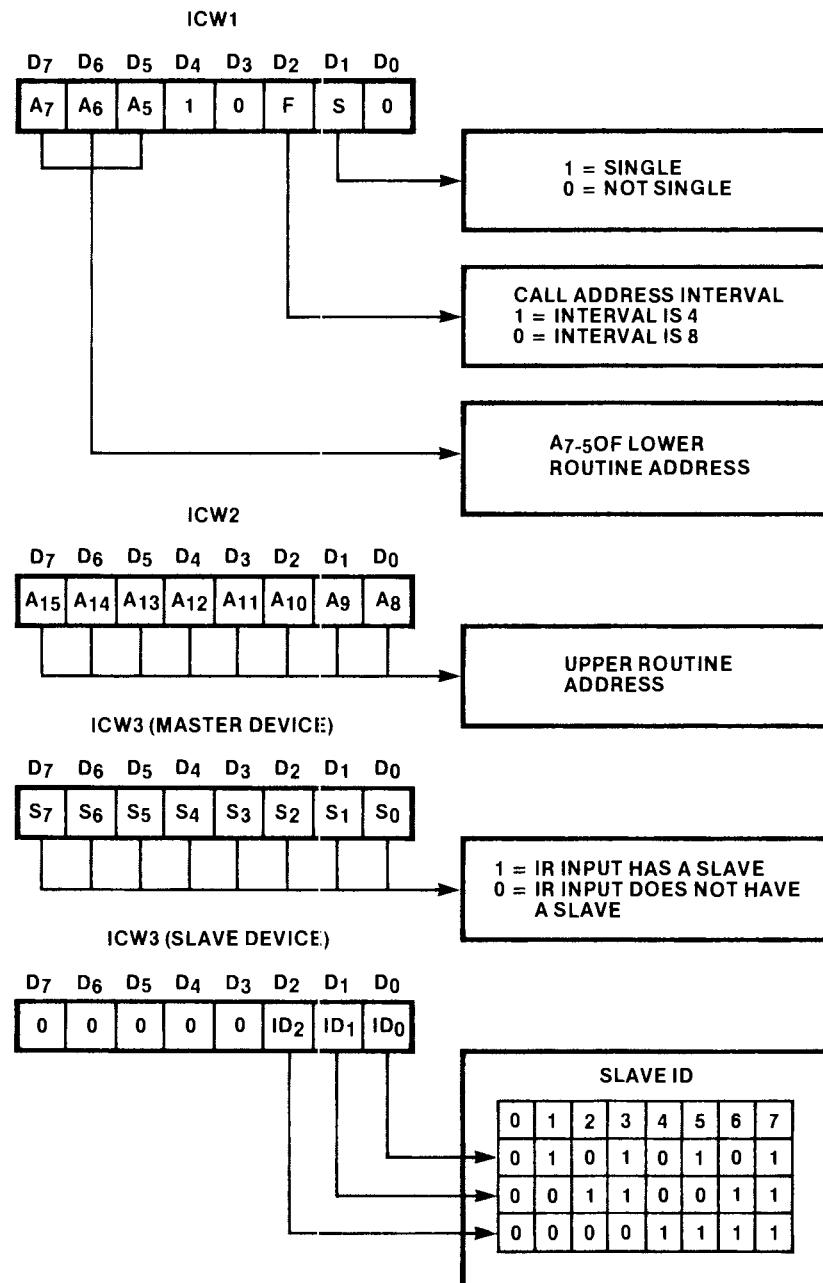

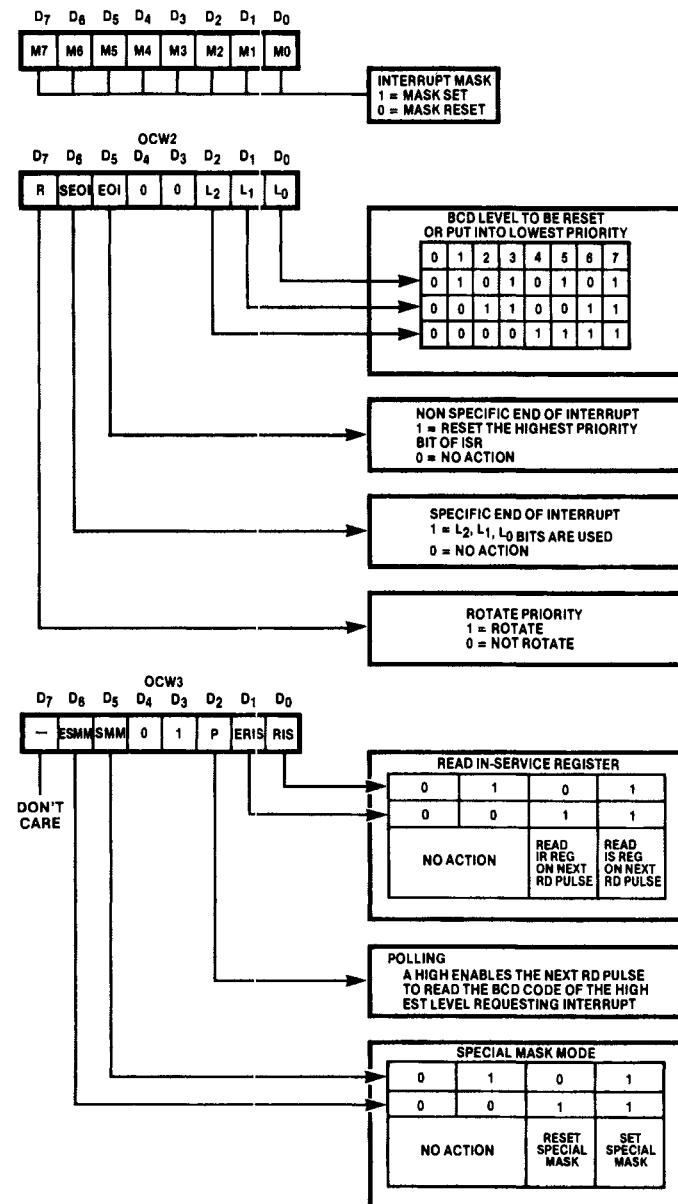

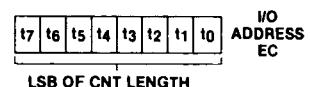

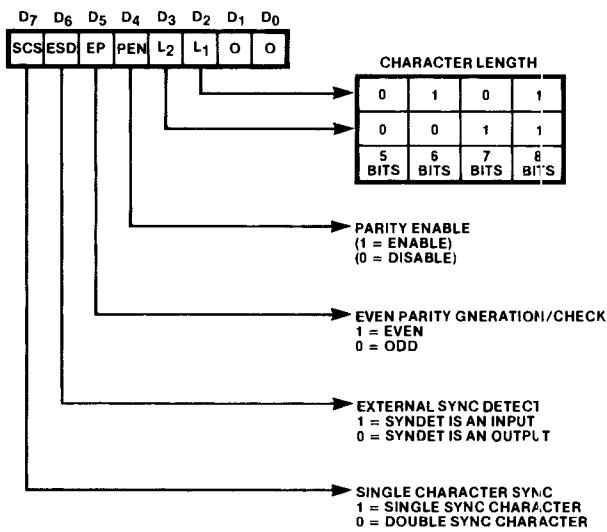

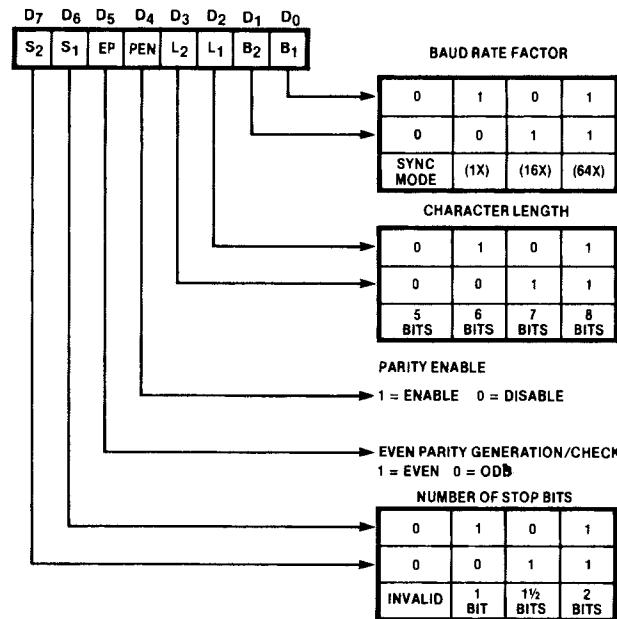

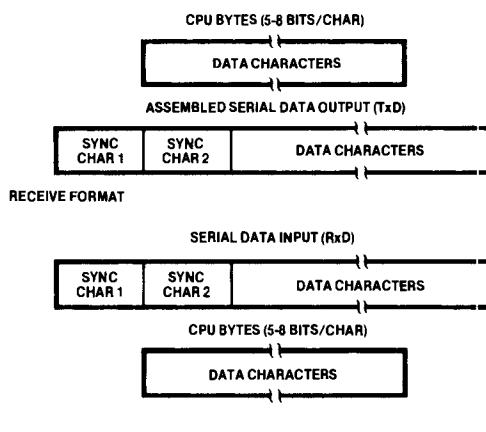

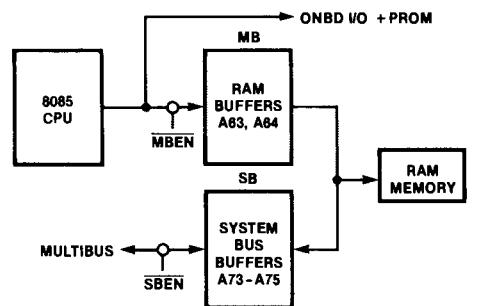

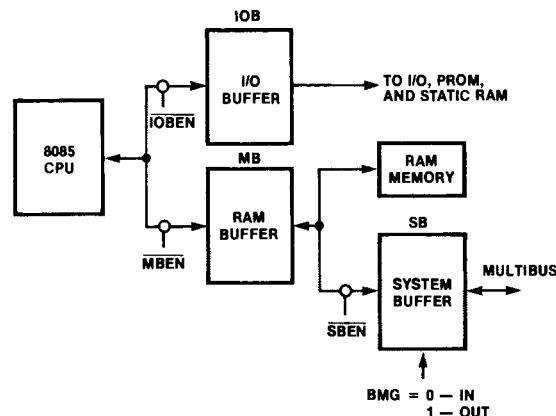

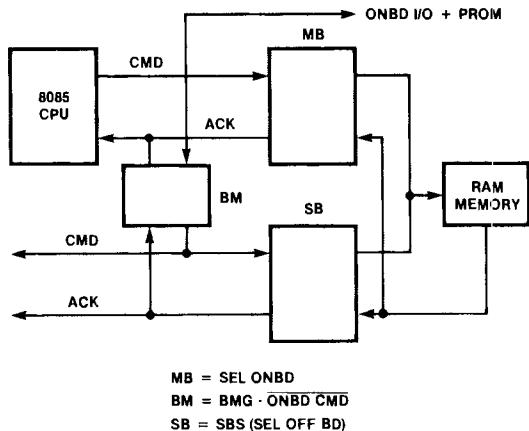

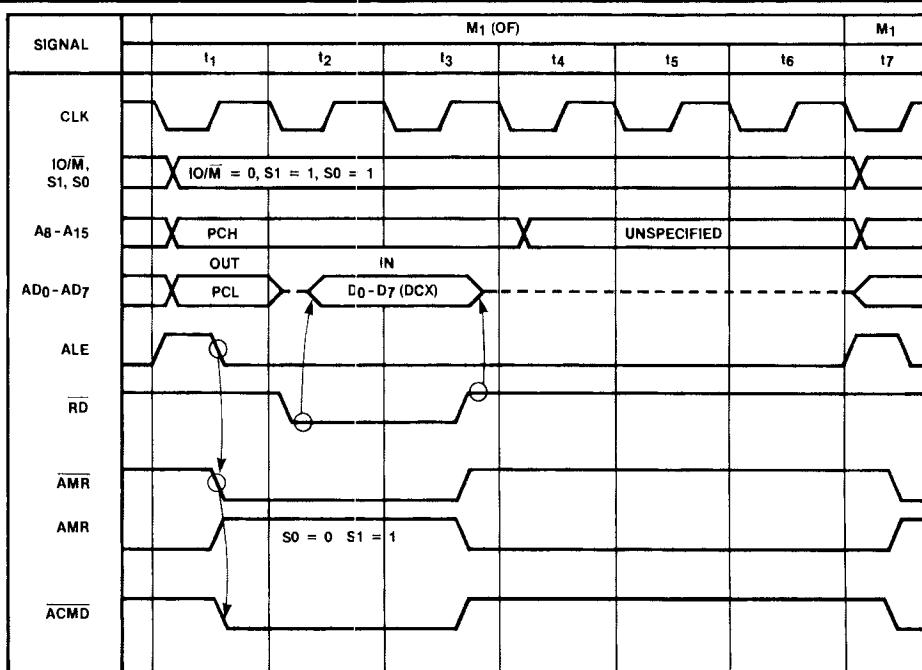

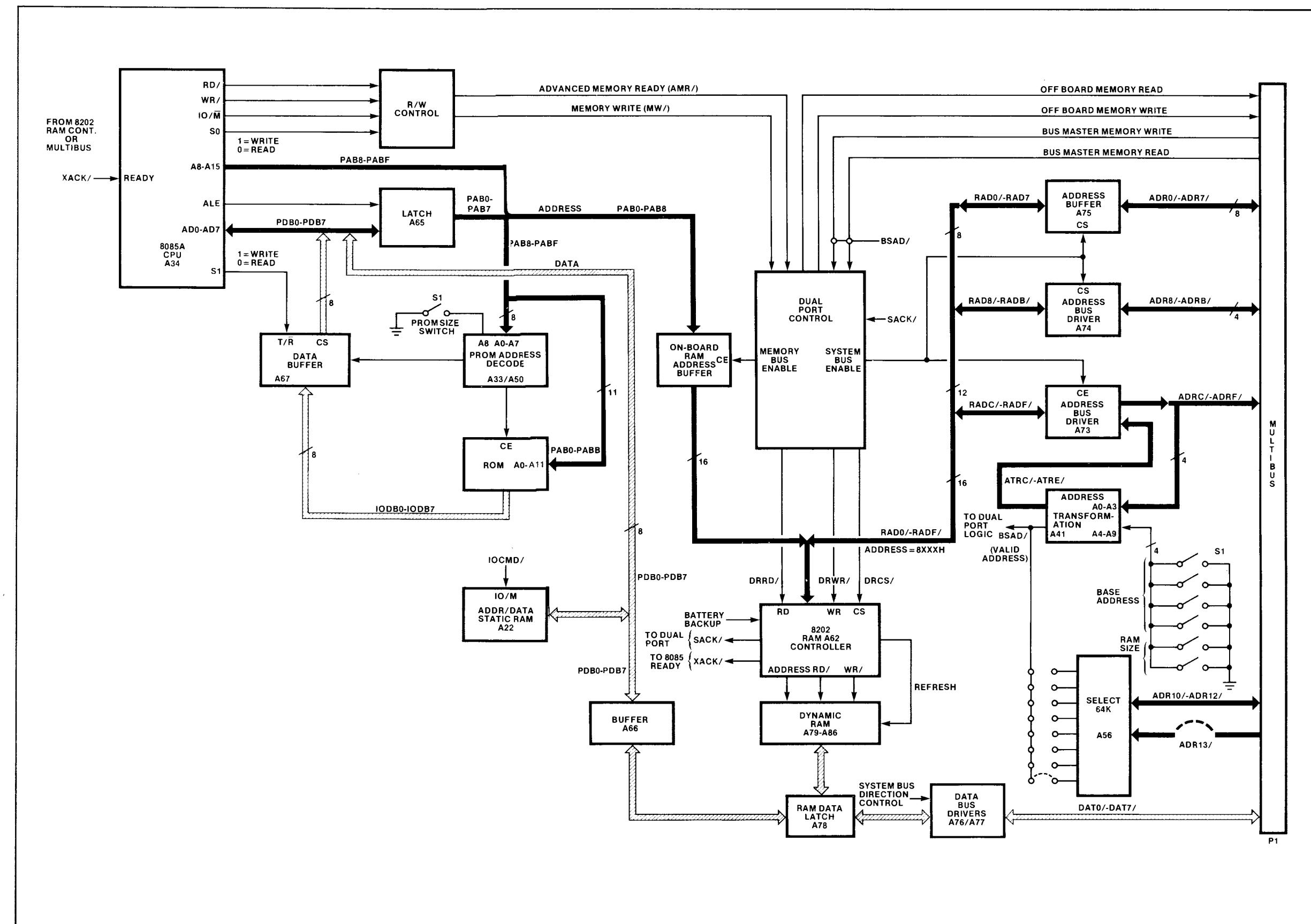

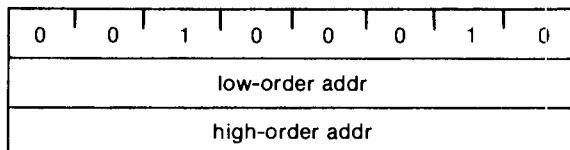

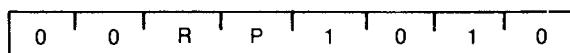

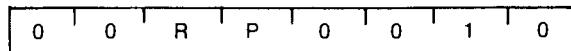

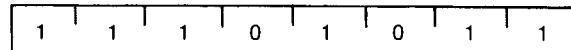

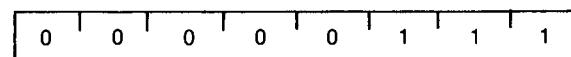

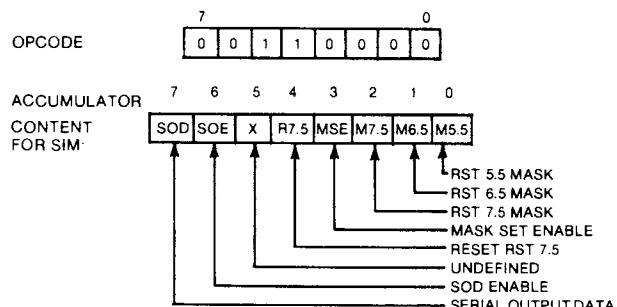

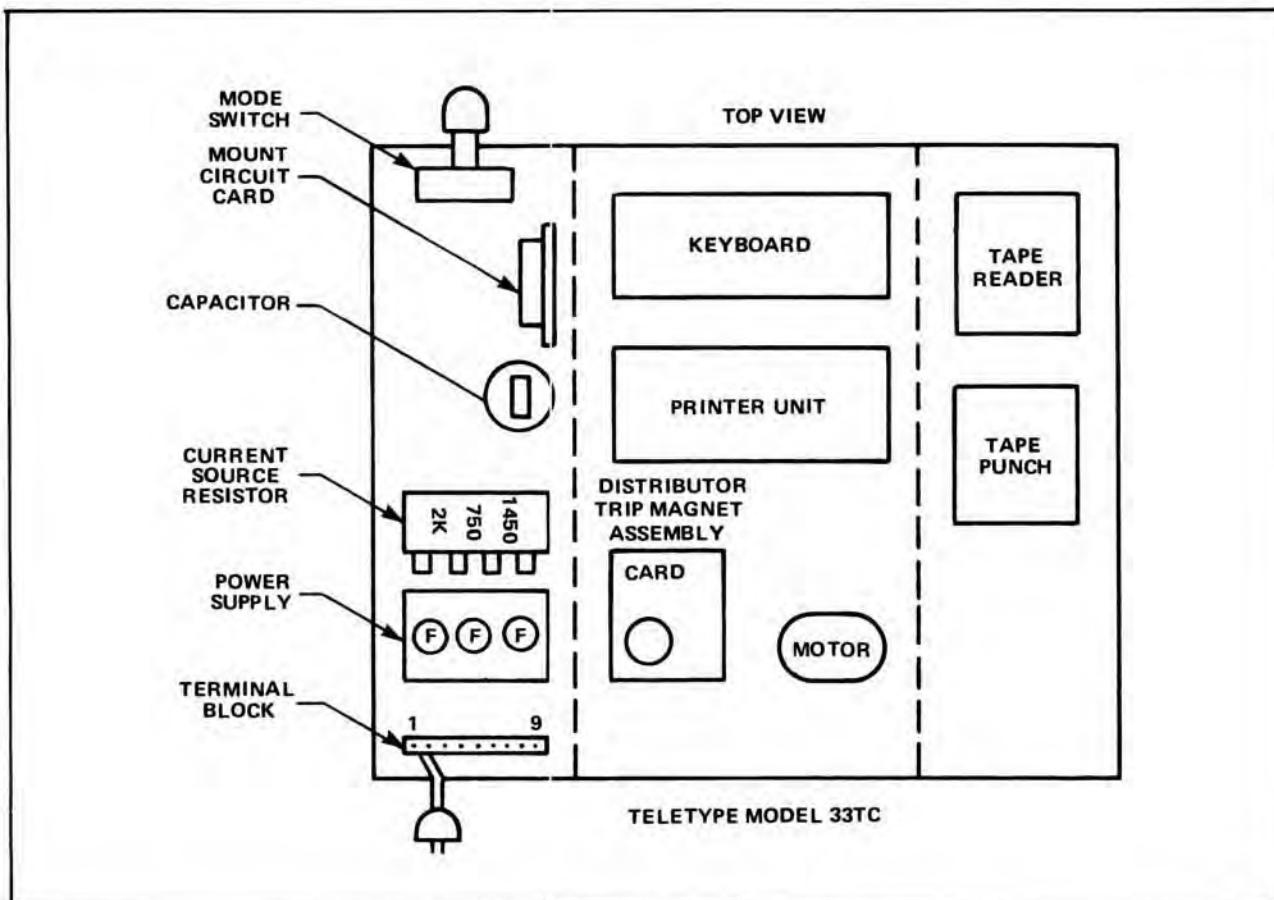

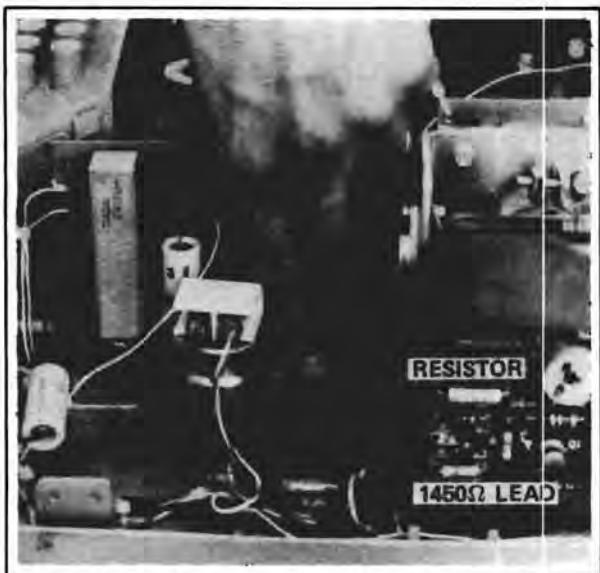

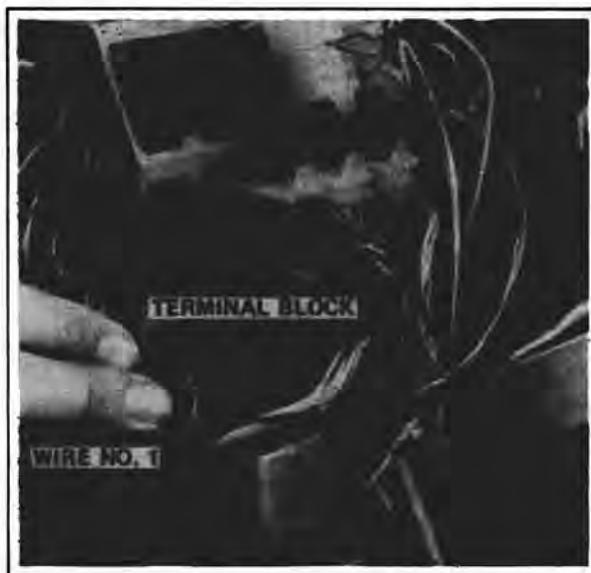

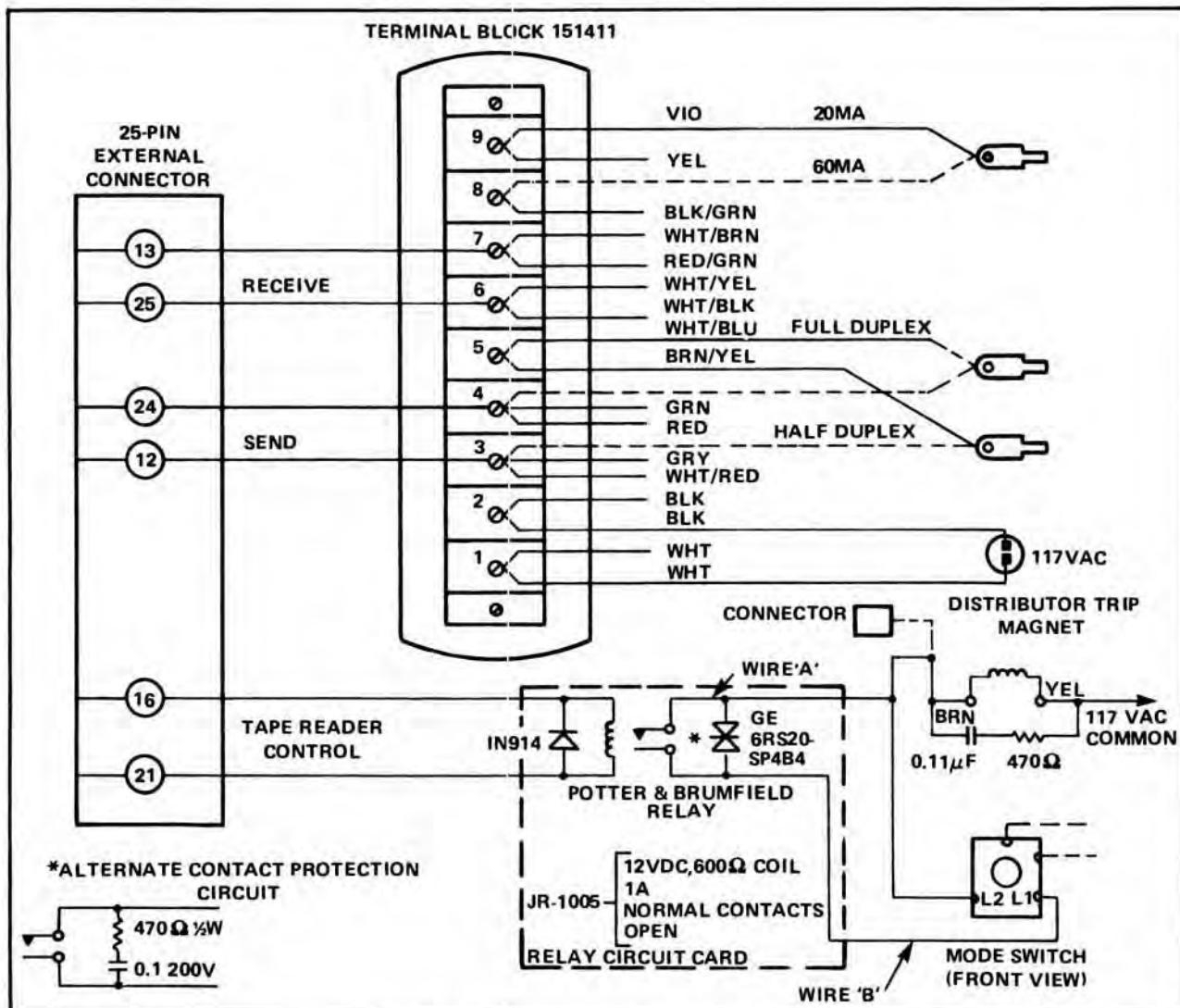

| 1 1                              | NA                      |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                |              |      |  |      |         |      |         |      |         |      |                         |                |          |     |  |     |    |     |    |     |     |     |    |